GVT7C1366A

GVT7C1366A is 256K X 36/512K X 18 Pipelined SRAM manufactured by Cypress.

- Part of the GVT71256C36 comparator family.

- Part of the GVT71256C36 comparator family.

( DataSheet : .. )

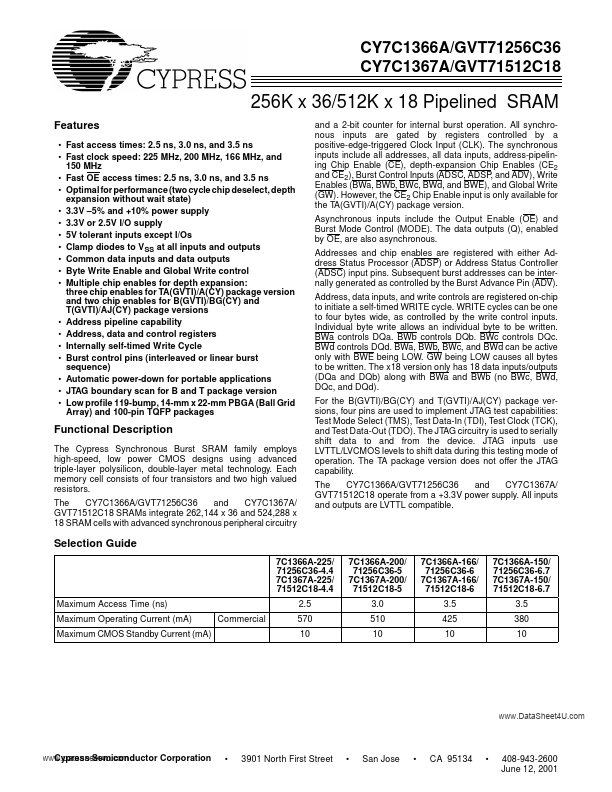

CY7C1366A/GVT71256C36 CY7C1367A/GVT71512C18

256K x 36/512K x 18 Pipelined SRAM

Features

- Fast access times: 2.5 ns, 3.0 ns, and 3.5 ns

- Fast clock speed: 225 MHz, 200 MHz, 166 MHz, and 150 MHz

- Fast OE access times: 2.5 ns, 3.0 ns, and 3.5 ns

- Optimal for performance (two cycle chip deselect, depth expansion without wait state)

- 3.3V

- 5% and +10% power supply

- 3.3V or 2.5V I/O supply

- 5V tolerant inputs except I/Os

- Clamp diodes to V SS at all inputs and outputs

- mon data inputs and data outputs

- Byte Write Enable and Global Write control

- Multiple chip enables for depth expansion: three chip enables for TA(GVTI)/A(CY) package version and...