Datasheet Summary

..

10/100 Mbps Fast Ethernet Physical Layer Single Chip Transceiver 1. General Description

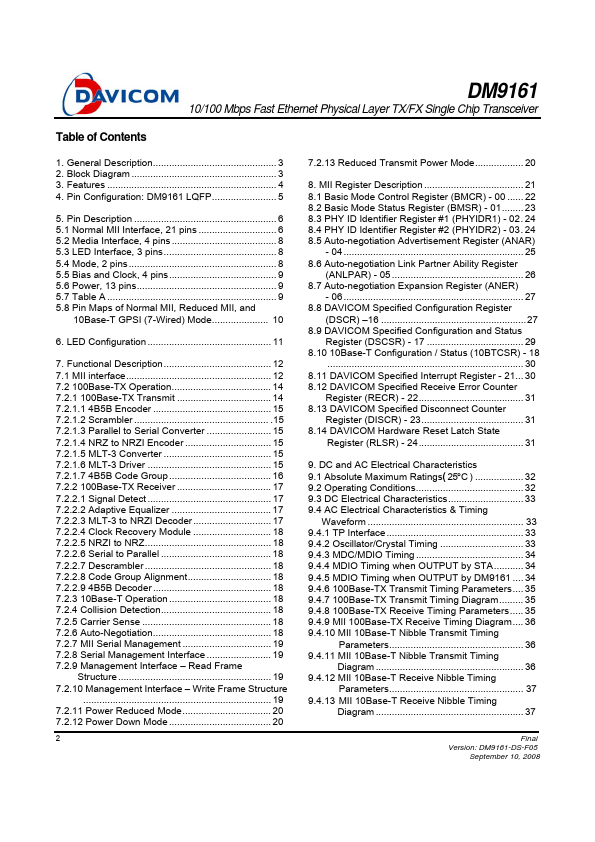

The DM9161 is a physical layer, single-chip, and low power transceiver for 100BASE-TX and 10BASE-T operations. On the media side, it provides a direct interface either to Unshielded Twisted Pair Category 5 Cable (UTP5) for 100BASE-TX Fast Ethernet, or UTP5/UTP3 Cable for 10BASE-T Ethernet. Through the Media Independent Interface (MII), the DM9161 connects to the Medium Access Control (MAC) layer, ensuring a high inter operability from different vendors. The DM9161 uses a low power and high performance CMOS process. It contains the entire physical layer functions of 100BASE-TX...