DM9000 Overview

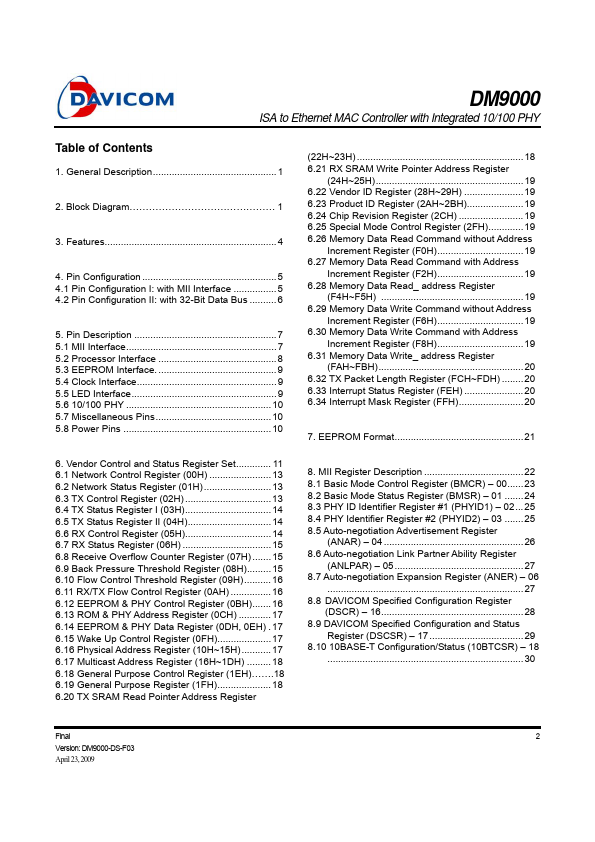

DM9000 ISA to Ethernet MAC Controller with Integrated 10/100 PHY The DM9000 is a fully integrated and cost-effective single chip Fast Ethernet MAC controller with a general processor interface, a 10/100M PHY and 4K Dword SRAM. It is designed with low power and high performance process that support 3.3V with 5V tolerance. The DM9000 also provides a MII interface to connect HPNA device or other transceivers that...