Key Specifications

Package: TSSOP

Mount Type: Surface Mount

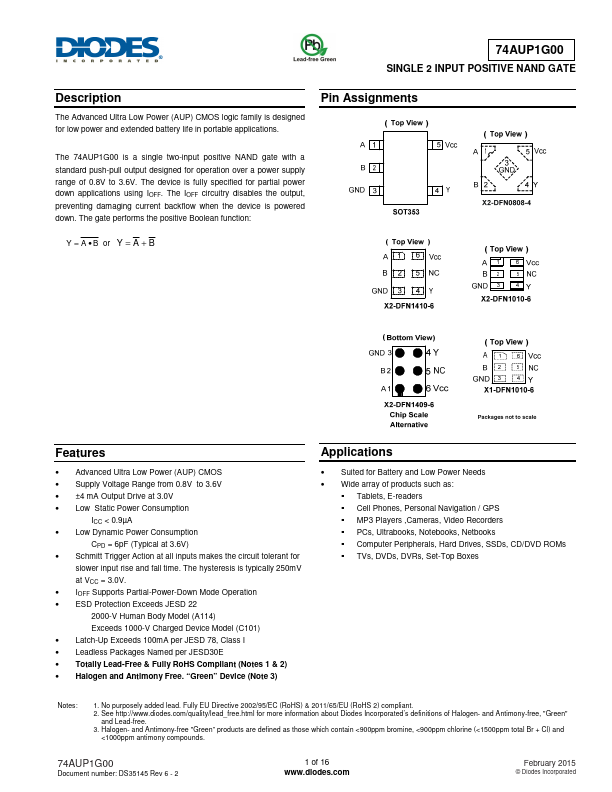

Pins: 5

Operating Voltage: 1.8 V

Max Voltage (typical range): 3.6 V

Min Voltage (typical range): 800 mV

Logic Function: NAND

Length: 2.05 mm

Width: 1.25 mm

Max Operating Temp: 125 °C

Min Operating Temp: -40 °C

| Part | 74AUP1G00 |

|---|---|

| Description | SINGLE 2 INPUT POSITIVE NAND GATE |

| Manufacturer | Diodes Incorporated |

| Size | 329.36 KB |

SINGLE 2 INPUT POSITIVE NAND GATE

Pricing from 0.1461 USD, available from Verical and Rochester Electronics.

Powered by Octopart

Price & Availability

| Seller | Price Breaks | Buy |

|---|---|---|

| Verical | 2567+ : 0.1461 USD 10000+ : 0.1303 USD 100000+ : 0.1091 USD |

View Offer |

| Rochester Electronics | 100+ : 0.1408 USD 500+ : 0.1267 USD 1000+ : 0.1169 USD 10000+ : 0.1042 USD |

View Offer |