Datasheet Summary

..

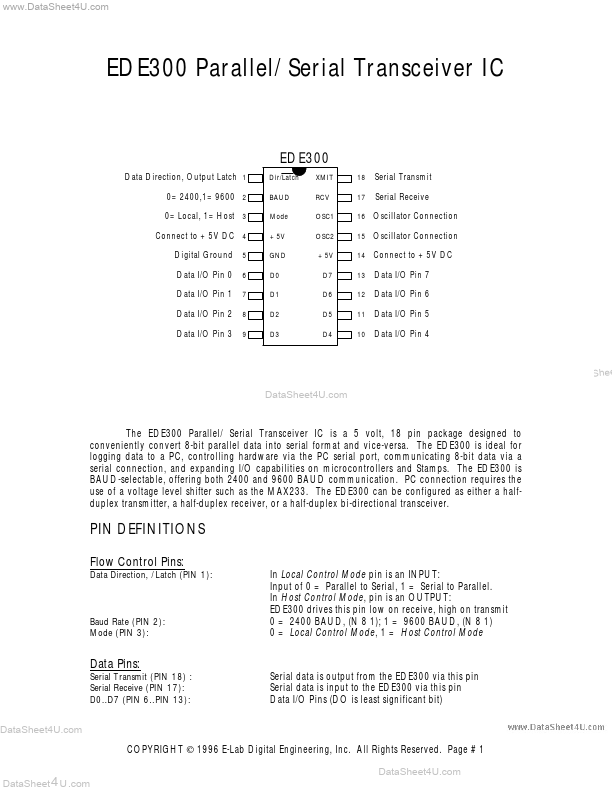

EDE300 Parallel/ Serial Transceiver IC

Data Direction, Output Latch 1 0=2400,1=9600 2 0=Local, 1=Host 3 Connect to +5V DC 4 Digital Ground Data I/O Pin 0 Data I/O Pin 1 Data I/O Pin 2 Data I/O Pin 3

5 6 7 8 9 Dir/Latch BAUD Mode +5V GND D0 D1 D2 D3 XMIT RCV OSC1 OSC2 +5V D7 D6 D5 D4 18 17 16 15 14 13 12 11 10

Serial Transmit Serial Receive Oscillator Connection Oscillator Connection Connect to +5V DC Data I/O Pin 7 Data I/O Pin 6 Data I/O Pin 5 Data I/O Pin 4

DataShee

.

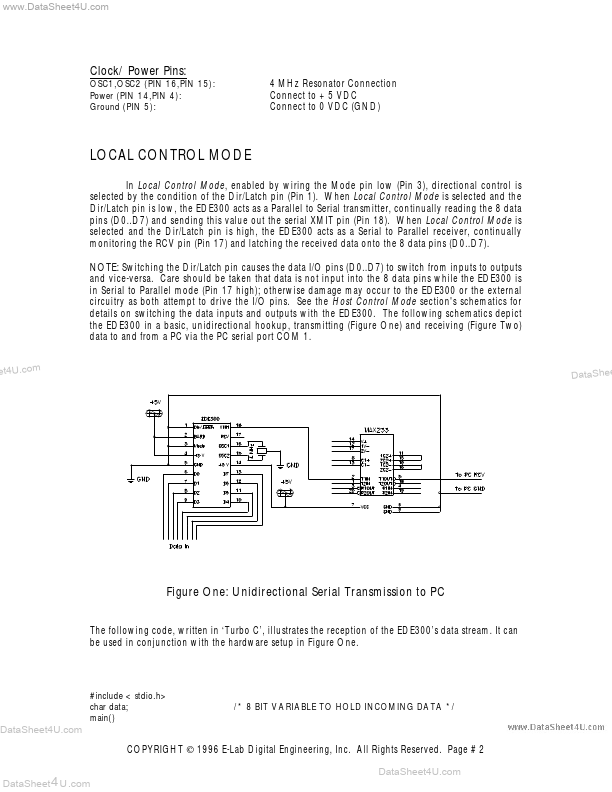

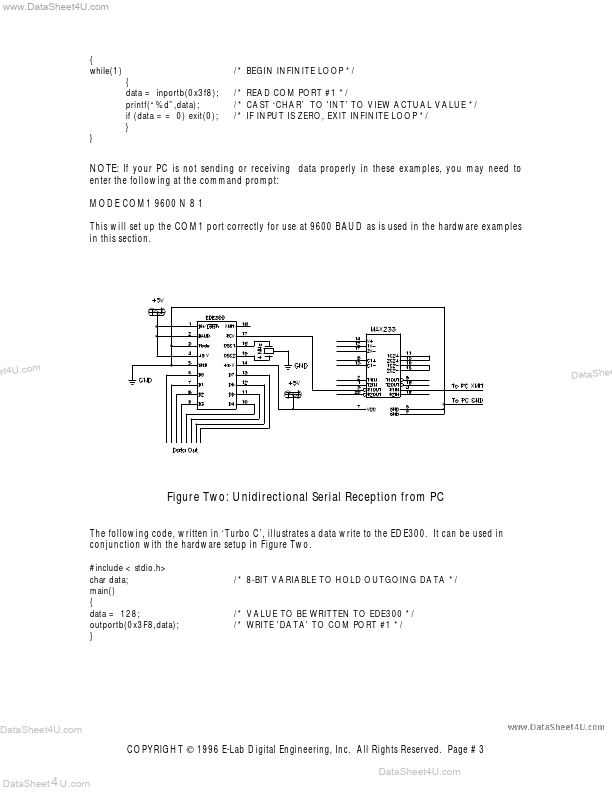

The EDE300 Parallel/ Serial Transceiver IC is a 5 volt, 18 pin package designed to conveniently convert 8-bit parallel data into serial format and vice-versa. The EDE300 is...