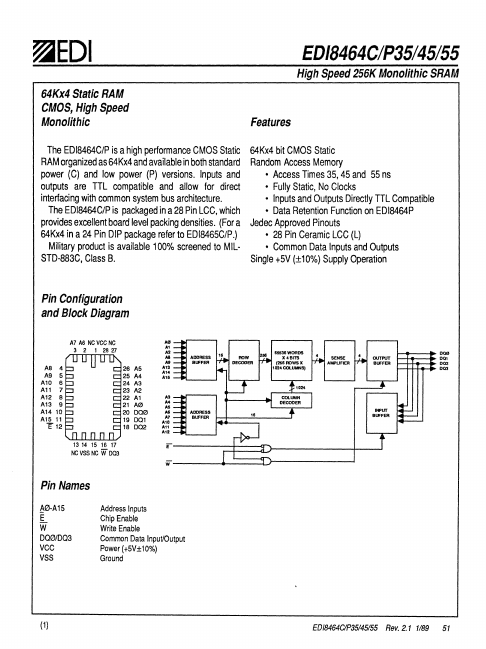

EDI8464C Overview

~EDI 64Kx4 Static RAM CMOS, High Speed Monolithic EDI8464CIP35145155 High Speed 256K Monolithic SRAM.

EDI8464C Key Features

- Access Times 35, 45 and 55 ns

- Fully Static, No Clocks

- Inputs and Outputs Directly TTL patible

- Data Retention Function on EDI8464P

- 28 Pin Ceramic LCC (L)

- mon Data Inputs and Outputs