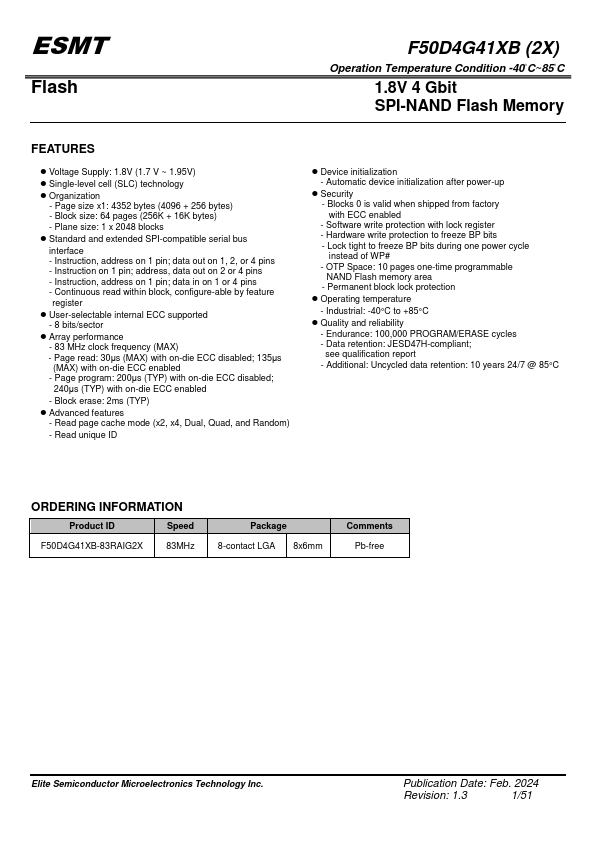

F50D4G41XB Overview

Key Features

- Voltage Supply: 1.8V (1.7 V ~ 1.95V)

- Single-level cell (SLC) technology

- Organization

- Page size x1: 4352 bytes (4096 + 256 bytes)

- Block size: 64 pages (256K + 16K bytes)

- Plane size: 1 x 2048 blocks

- Standard and extended SPI-compatible serial bus interface

- Instruction, address on 1 pin; data out on 1, 2, or 4 pins

- Instruction on 1 pin; address, data out on 2 or 4 pins

- Instruction, address on 1 pin; data in on 1 or 4 pins