M54D2G16128A

Feature

- JEDEC LPDDR2‐S4B pliance

- HSUL_12 interface (High Speed Unterminated Logic 1.2V)

- Power supply:

- VDD1 = 1.7 to 1.95V

- VDD2, VDDCA, VDDQ = 1.14 to 1.3V

- 4n prefetch architecture

- Multiplexed, double data rate, mand/address inputs; mands entered on every CK edge

- Bidirectional/differential data strobe per byte of data (DQS_t/DQS_c)

- Programmable read latency (RL) and write latency (WL)

- Programmable burst lengths (BL): 4, 8, 16

- Pre-bank refresh for concurrent operation

- Partial Array Self Refresh (PASR)

- Temperature pensated Self Refresh (TCSR) by built‐in temperature sensor

- Deep Power Down mode (DPD)

- Programmable Driver Strength (DS)

- Clock stop capability

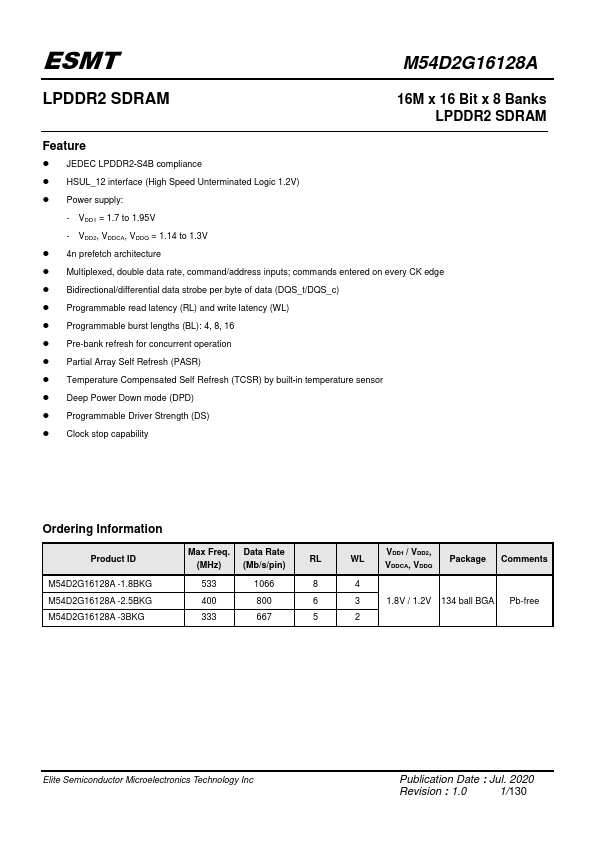

Ordering Information

Product ID

M54D2G16128A -1.8BKG M54D2G16128A -2.5BKG M54D2G16128A -3BKG

Max Freq. Data Rate RL

(MHz) (Mb/s/pin)

VDD1 / VDD2,

Package ments

VDDCA, VDDQ

1.8V / 1.2V 134 ball BGA Pb-free

Elite Semiconductor Microelectronics...