Datasheet Summary

..

Bt8110/8110B

High-Capacity ADPCM Processor

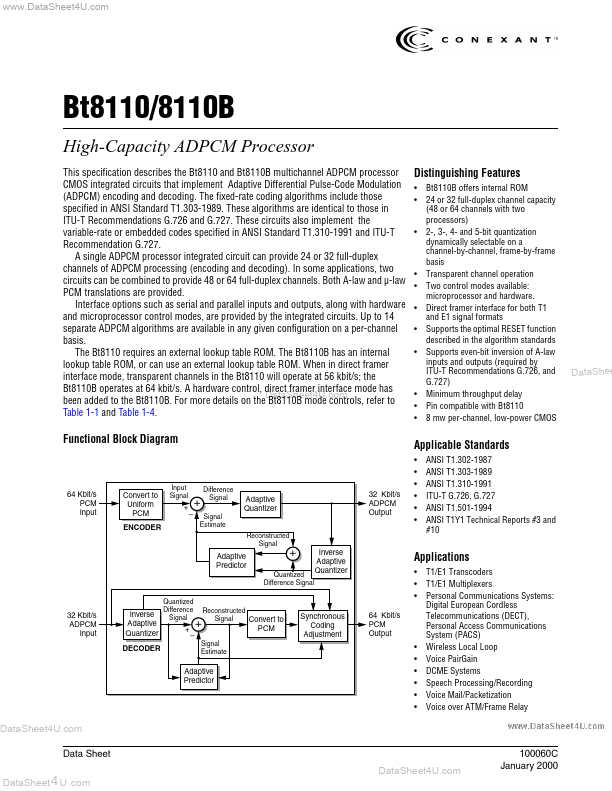

This specification describes the Bt8110 and Bt8110B multichannel ADPCM processor CMOS integrated circuits that implement Adaptive Differential Pulse-Code Modulation (ADPCM) encoding and decoding. The fixed-rate coding algorithms include those specified in ANSI Standard T1.303-1989. These algorithms are identical to those in ITU-T Remendations G.726 and G.727. These circuits also implement the variable-rate or embedded codes specified in ANSI Standard T1.310-1991 and ITU-T Remendation G.727. A single ADPCM processor integrated circuit can provide 24 or 32 full-duplex channels of ADPCM processing (encoding and decoding)....