Datasheet Summary

TMC Description

TM50S116T SDRAM

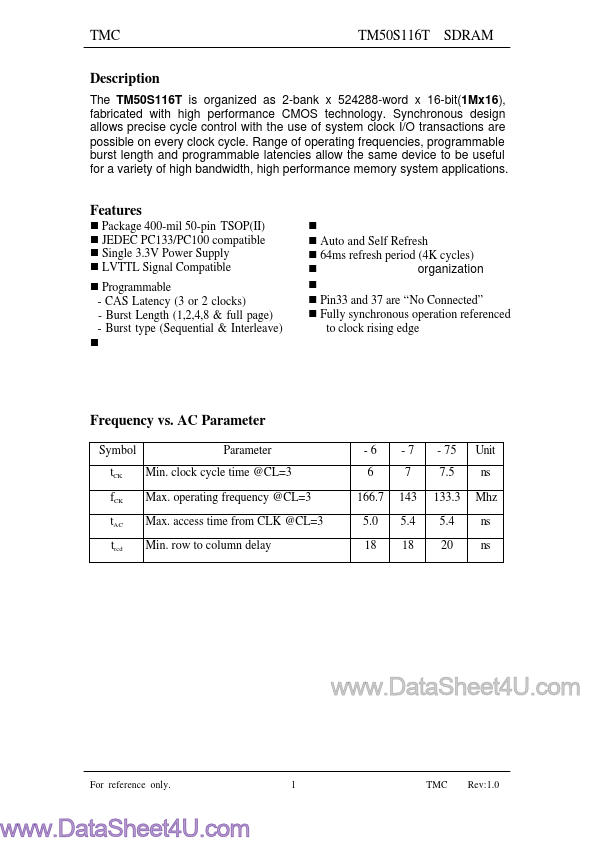

The TM50S116T is organized as 2-bank x 524288-word x 16-bit(1Mx16), fabricated with high performance CMOS technology. Synchronous design allows precise cycle control with the use of system clock I/O transactions are possible on every clock cycle. Range of operating frequencies, programmable burst length and programmable latencies allow the same device to be useful for a variety of high bandwidth, high performance memory system applications.

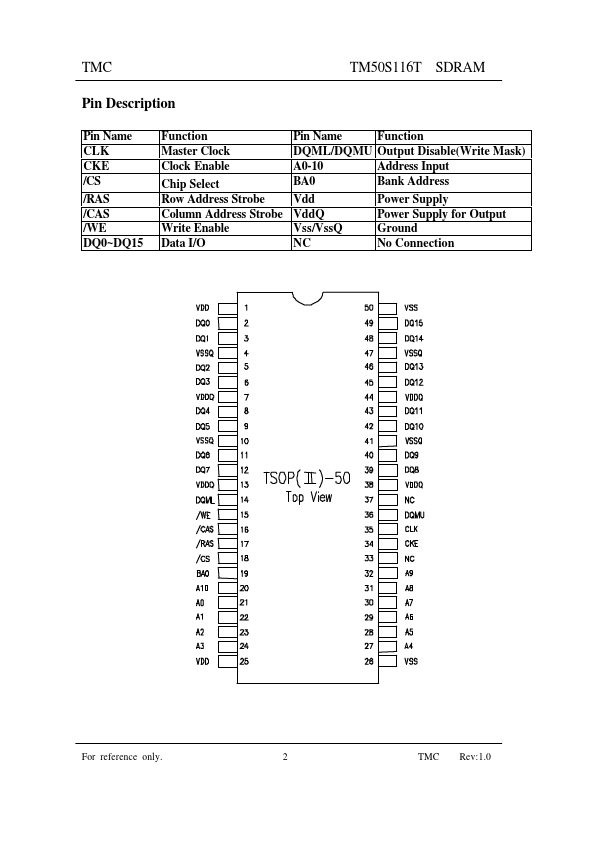

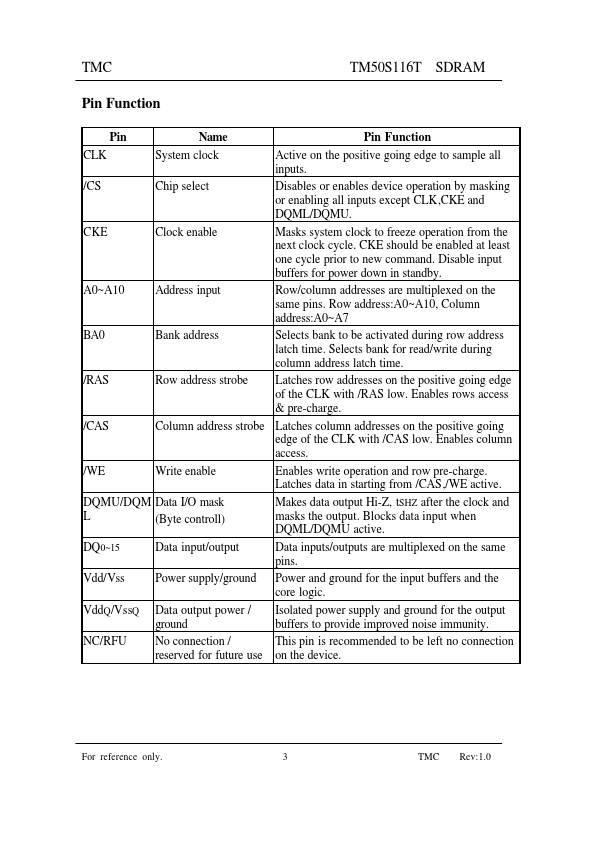

Features n Package 400-mil 50-pin TSOP(II) n JEDEC PC133/PC100 patible n Single 3.3V Power Supply n LVTTL Signal patible n Byte control(DQML and DQMU) n Auto and Self Refresh n 64ms refresh period (4K cycles) n...