EDS2504APTA-75

EDS2504APTA-75 is 256M bits SDRAM manufactured by Elpida Memory.

cription

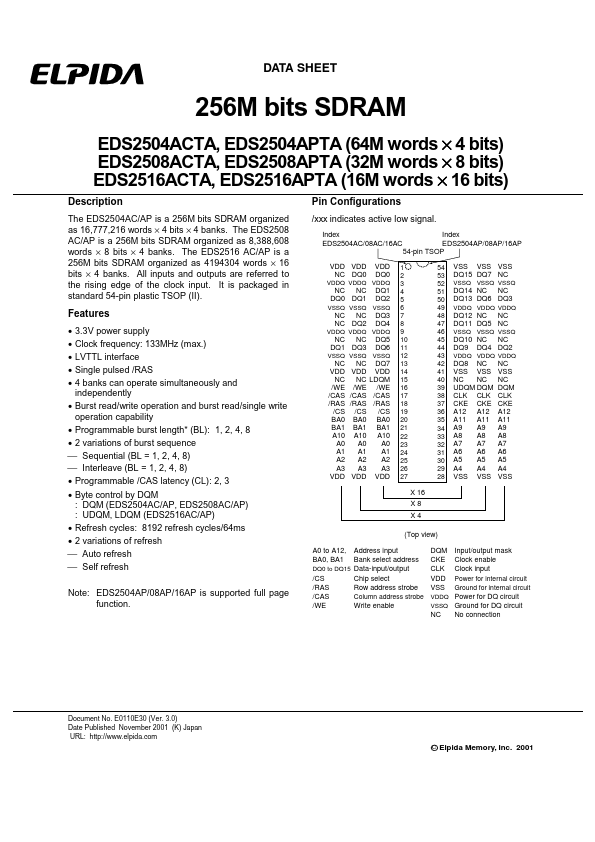

The EDS2504AC/AP is a 256M bits SDRAM organized as 16,777,216 words × 4 bits × 4 banks. The EDS2508 AC/AP is a 256M bits SDRAM organized as 8,388,608 words × 8 bits × 4 banks. The EDS2516 AC/AP is a 256M bits SDRAM organized as 4194304 words × 16 bits × 4 banks. All inputs and outputs are referred to the rising edge of the clock input. It is packaged in standard 54-pin plastic TSOP (II).

Pin Configurations

/xxx indicates active low signal.

Index EDS2504AC/08AC/16AC VDD VDD NC DQ0 NC NC DQ0 DQ1 NC NC NC DQ2 NC NC DQ1 DQ3 NC VDD NC /WE /CAS /RAS /CS BA0 BA1 A10 A0 A1 A2 A3 VDD VDD DQ0 DQ1 DQ2 DQ3 DQ4 DQ5 DQ6 Index EDS2504AP/08AP/16AP 54-pin TSOP

54 53 52 51 50 49 48 47 46 45 44 43 42 41 40 39 38 37 36 35 34 33 32 31 30 29 28

VDDQ VDDQ VDDQ

Features

- -

- -

- 3.3V power supply Clock frequency: 133MHz (max.) LVTTL interface Single pulsed /RAS 4 banks can operate simultaneously and independently

- Burst read/write operation and burst read/single write operation capability

- Programmable burst length- (BL): 1, 2, 4, 8

- 2 variations of burst sequence Sequential (BL = 1, 2, 4, 8) Interleave (BL = 1, 2, 4, 8)

- Programmable /CAS latency (CL): 2, 3

- Byte control by DQM : DQM (EDS2504AC/AP, EDS2508AC/AP) : UDQM, LDQM (EDS2516AC/AP)

- Refresh cycles: 8192 refresh cycles/64ms

- 2 variations of refresh Auto refresh Self refresh Note: EDS2504AP/08AP/16AP is supported full page function.

VSSQ VSSQ VSSQ

VDDQ VDDQ VDDQ

VSSQ VSSQ VSSQ

NC DQ7 VDD VDD NC LDQM /WE /WE /CAS /CAS /RAS /RAS /CS /CS BA0 BA0 BA1 BA1 A10 A10 A0 A0 A1 A1 A2 A2 A3 A3 VDD VDD

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27

VSS VSS VSS DQ15 DQ7 NC

VSSQ VSSQ VSSQ

DQ14 NC NC DQ13 DQ6 DQ3

VDDQ VDDQ VDDQ

DQ12 NC NC DQ11 DQ5 NC

VSSQ VSSQ VSSQ

DQ10 NC NC DQ9 DQ4...