S1216AATA-75-E

S1216AATA-75-E is EDS1216AATA-75-E manufactured by Elpida Memory.

Description

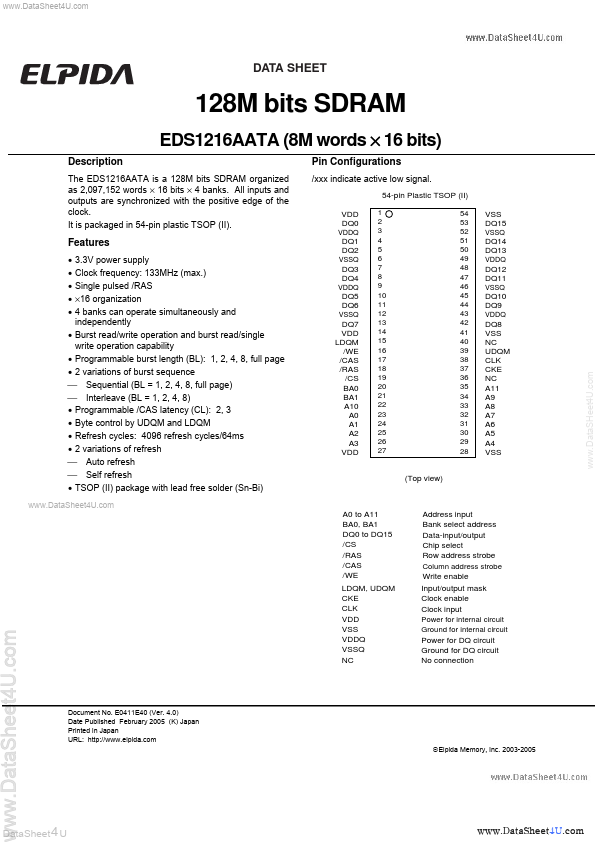

The EDS1216AATA is a 128M bits SDRAM organized as 2,097,152 words × 16 bits × 4 banks. All inputs and outputs are synchronized with the positive edge of the clock. It is packaged in 54-pin plastic TSOP (II).

Pin Configurations

/xxx indicate active low signal.

54-pin Plastic TSOP (II) VDD DQ0

VDDQ

Features

- -

- -

- 3.3V power supply Clock frequency: 133MHz (max.) Single pulsed /RAS ×16 organization 4 banks can operate simultaneously and independently

- Burst read/write operation and burst read/single write operation capability

- Programmable burst length (BL): 1, 2, 4, 8, full page

- 2 variations of burst sequence Sequential (BL = 1, 2, 4, 8, full page) Interleave (BL = 1, 2, 4, 8)

- Programmable /CAS latency (CL): 2, 3

- Byte control by UDQM and LDQM

- Refresh cycles: 4096 refresh cycles/64ms

- 2 variations of refresh Auto refresh Self refresh

- TSOP (II) package with lead free solder (Sn-Bi)

..

DQ1 DQ2

VSSQ

DQ3 DQ4

VDDQ

DQ5 DQ6

VSSQ

(Top view) ww..

A0 to A11 BA0, BA1 DQ0 to DQ15 /CS /RAS /CAS /WE LDQM, UDQM CKE CLK VDD VSS VDDQ VSSQ NC

Address input Bank select address Data-input/output Chip select Row address strobe

Column address strobe

Write enable Input/output mask Clock enable Clock input

Power for internal circuit Ground for internal circuit

Power for DQ circuit Ground for DQ circuit No connection

Document No. E0411E40 (Ver. 4.0) Date Published February 2005 (K) Japan Printed in Japan URL: http://.elpida. Elpida Memory, Inc. 2003-2005

Data Sheet 4 U .

. .. 4U.

..

DQ7 VDD LDQM /WE /CAS /RAS /CS BA0 BA1 A10 A0 A1 A2 A3 VDD

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27

54 53 52 51 50 49 48 47 46 45 44 43 42 41 40 39 38 37 36 35 34 33 32 31 30 29 28

VSS...