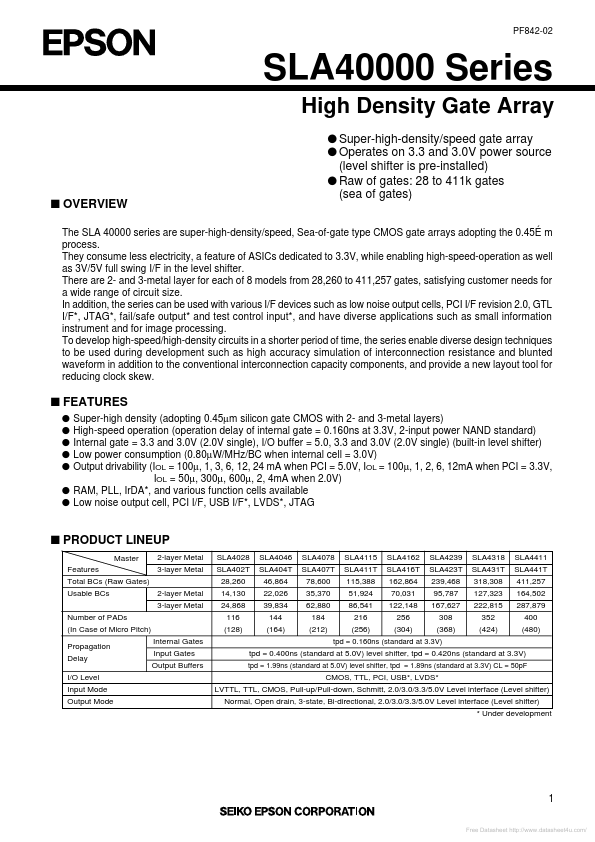

SLA4115 Description

PF842-02 SLA40000 Series High Density Gate Array q Super-high-density/speed gate array q Operates on 3.3 and 3.0V power source (level shifter is pre-installed) q Raw of gates: 28 to 411k gates (sea of gates) s OVERVIEW The SLA 40000 series are super-high-density/speed, Sea-of-gate type CMOS gate arrays adopting the 0.45É m process. They consume less electricity,.