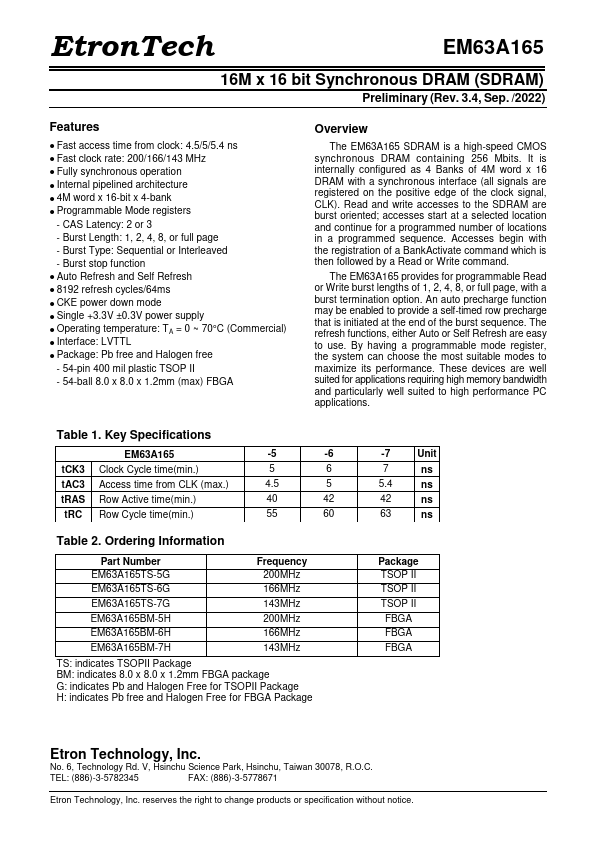

EM63A165 Key Features

- Fast access time from clock: 4.5/5/5.4 ns

- Fast clock rate: 200/166/143 MHz

- Fully synchronous operation

- Internal pipelined architecture

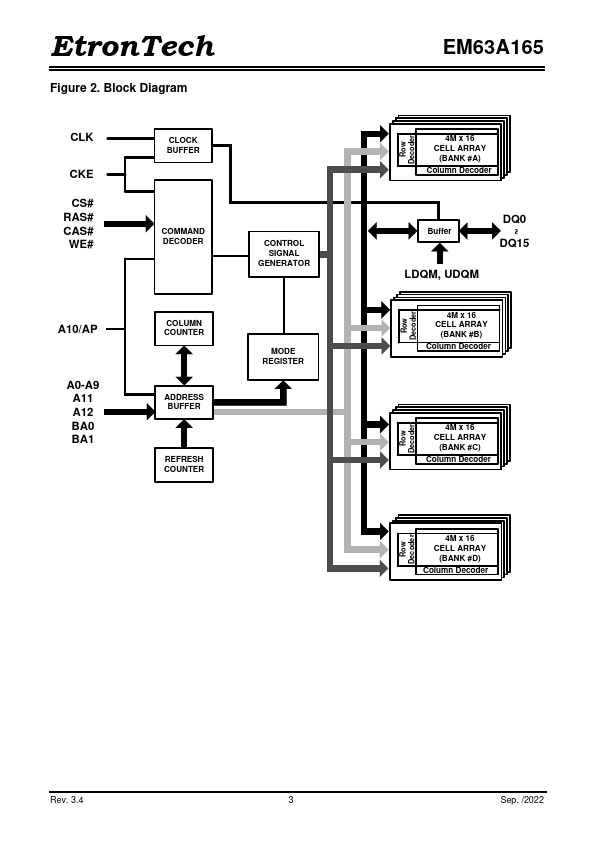

- 4M word x 16-bit x 4-bank

- Programmable Mode registers

- CAS Latency: 2 or 3

- Burst Length: 1, 2, 4, 8, or full page

- Burst Type: Sequential or Interleaved

- Burst stop function