CCD8091 Description

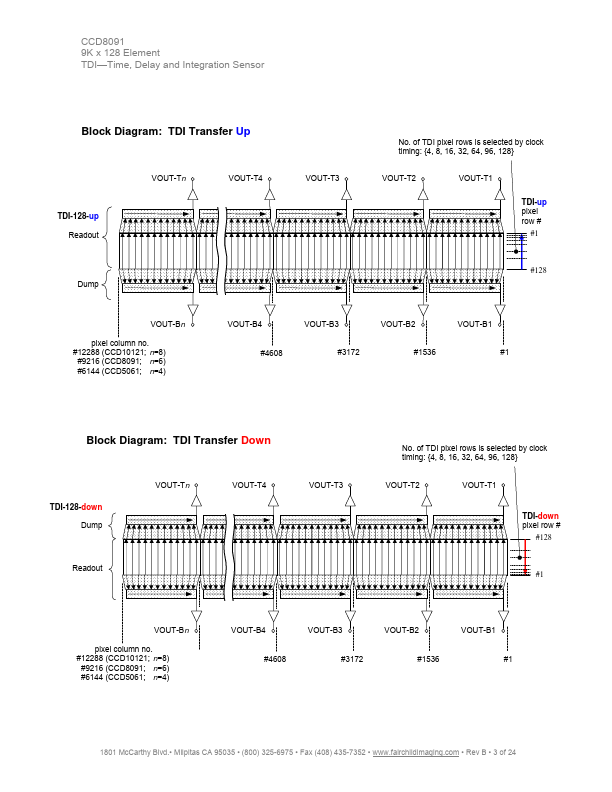

The CCD8091 is a 9216 pixel x 128 line, high speed TDI sensor. The active imaging area is organized as 9216 vertical columns and 128 horizontal TDI rows. The array is set up for bi-directional operation.

CCD8091 Key Features

- 9216 pixels per line

- Bi-directional TDI (shift up or down)

- 6 outputs

- each capable of 20MHz data rate

- 160MHz total data rate

- 100% fill factor

- 8.75µm x 8.75µm pixel size

- On-chip binning capability