74ABT2952

74ABT2952 is Octal Registered Transceiver manufactured by Fairchild Semiconductor.

74ABT2952 Octal Registered Transceiver

January 1992 Revised November 1999

74ABT2952 Octal Registered Transceiver

General Description

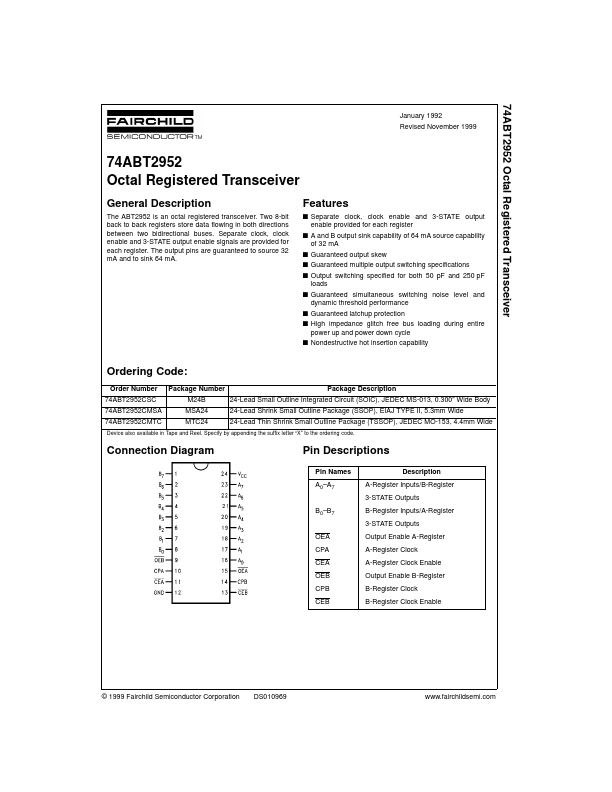

The ABT2952 is an octal registered transceiver. Two 8-bit back to back registers store data flowing in both directions between two bidirectional buses. Separate clock, clock enable and 3-STATE output enable signals are provided for each register. The output pins are guaranteed to source 32 mA and to sink 64 mA.

Features s Separate clock, clock enable and 3-STATE output enable provided for each register s A and B output sink capability of 64 mA source capability of 32 mA s Guaranteed output skew s Guaranteed multiple output switching specifications s...