74ACT825 Overview

Key Specifications

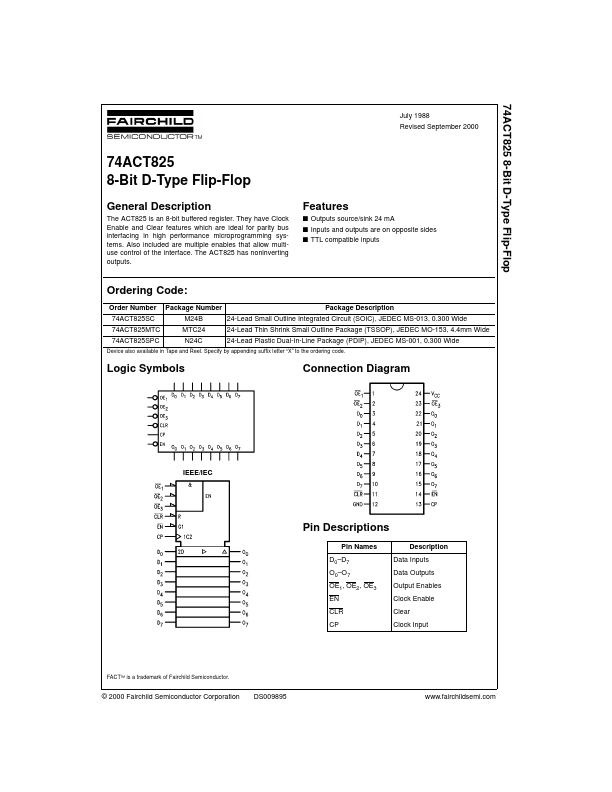

Package: SOP

Mount Type: Surface Mount

Pins: 24

Operating Voltage: 5 V

Description

The ACT825 is an 8-bit buffered register. They have Clock Enable and Clear features which are ideal for parity bus interfacing in high performance microprogramming systems.

Key Features

- Specify by appending suffix letter “X” to the ordering code