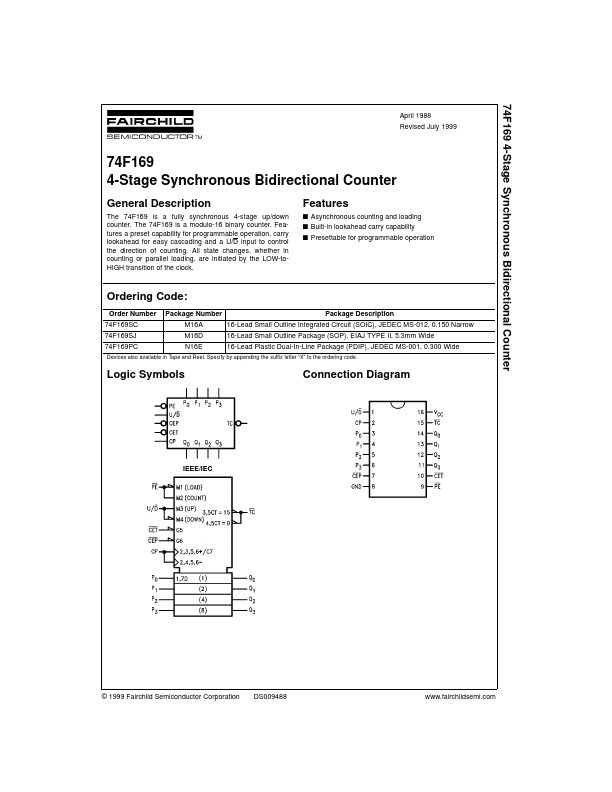

| Part | 74F169 |

|---|---|

| Description | 4-Stage Synchronous Bidirectional Counter |

| Manufacturer | Fairchild Semiconductor |

| Size | 66.78 KB |

Related Datasheets

| Part Number | Manufacturer | Description |

|---|---|---|

| 74F169 | National Semiconductor | 4-Stage Synchronous Bidirectional Counter |

| 74F169 | NXP Semiconductors | 4-bit up/down binary synchronous counter |

| 74F163A | National Semiconductor | Synchronous Presettable Binary Counter |

| 74F161A | National Semiconductor | Synchronous Presettable Binary Counter |

| 74F164A | National Semiconductor | Serial-In / Parallel-Out Shift Register |