74S280

Overview

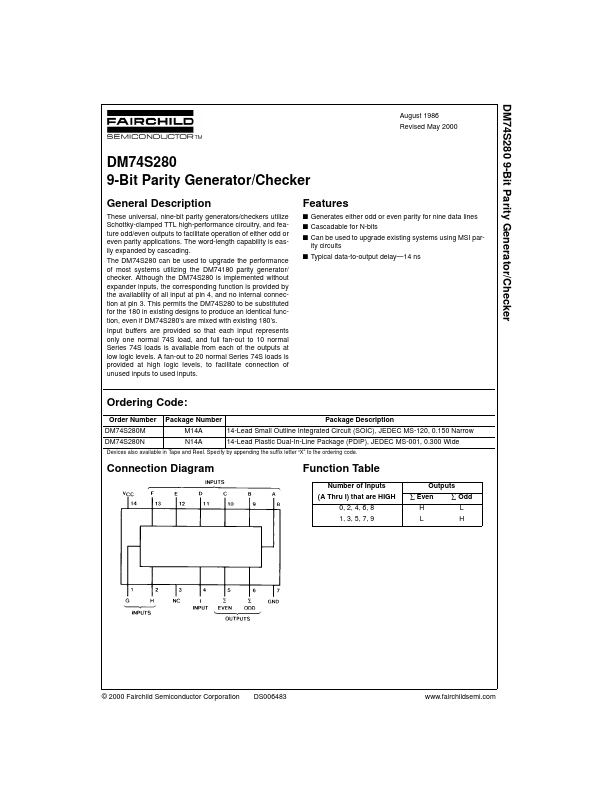

These universal, nine-bit parity generators/checkers utilize Schottky-clamped TTL high-performance circuitry, and feature odd/even outputs to facilitate operation of either odd or even parity applications. The word-length capability is easily expanded by cascading.

- This permits the DM74S280 to be substituted for the 180 in existing designs to produce an identical function, even if DM74S280’s are mixed with existing 180’s. Input buffers are provided so that each input represents only one normal 74S load, and full fan-out to 10 normal Series 74S loads is available from each of the outputs at low logic levels. A fan-out to 20 normal Series 74S loads is provided at high logic levels, to facilitate connection of unused inputs to used inputs. Features s Generates either odd or even parity for nine data lines s Cascadable for N-bits s Can be used to upgrade existing systems using MSI par- ity circuits s Typical data-to-output delay-14 ns Ordering Code: Order Number Package Number Package Description