74VCXR162601 Overview

Key Specifications

Package: SOP

Mount Type: Surface Mount

Pins: 56

Operating Voltage: 3.3 V

Description

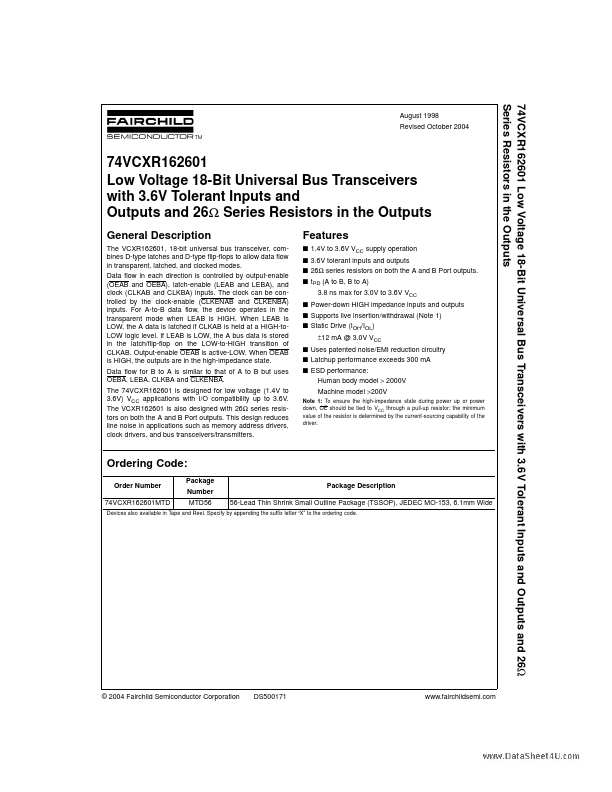

The VCXR162601, 18-bit universal bus transceiver, combines D-type latches and D-type flip-flops to allow data flow in transparent, latched, and clocked modes. Data flow in each direction is controlled by output-enable (OEAB and OEBA), latch-enable (LEAB and LEBA), and clock (CLKAB and CLKBA) inputs.

Key Features

- s 1.4V to 3.6V VCC supply operation s 3.6V tolerant inputs and outputs s 26Ω series resistors on both the A and B Port outputs