FIN1217 Description

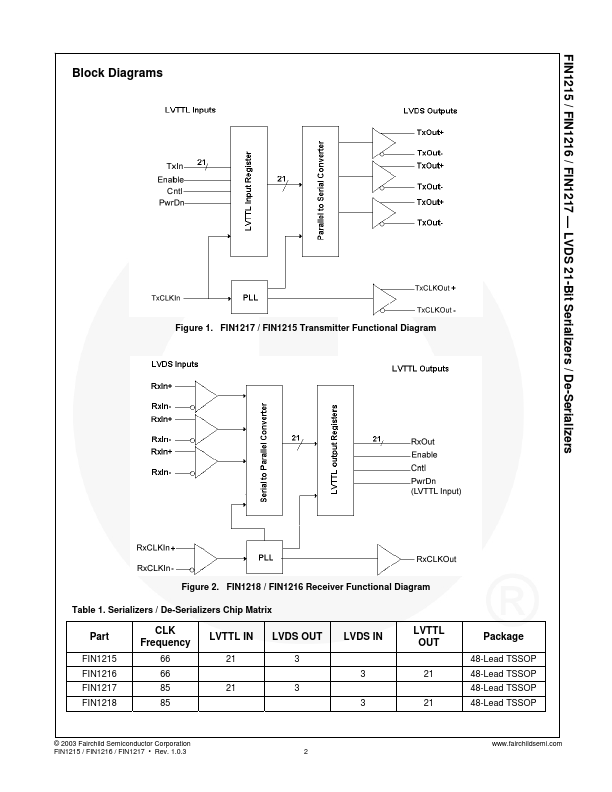

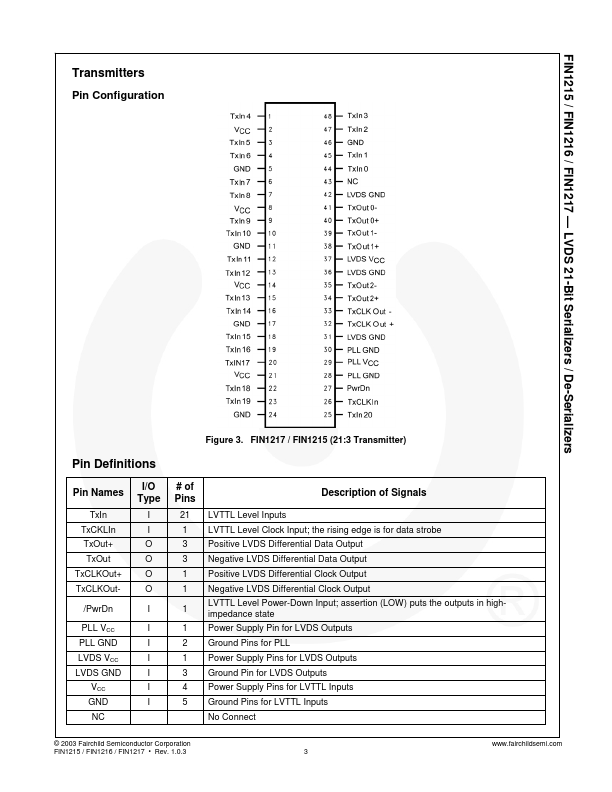

The FIN1217 and FIN1215 transform 21-bit wide parallel LVTTL (Low-Voltage TTL) data into three serial LVDS (Low-Voltage Differential Signaling) data streams. A phase-locked transmit clock is transmitted in parallel with the data stream over a separate LVDS link. Every cycle of transmit clock, 21 bits of input LVTTL data are sampled and transmitted.

FIN1217 Key Features

- Low Power Consumption

- 20MHz to 85MHz Shift Clock Support

- 50% Duty Cycle on the Clock Output of Receiver

- ±1V mon-mode Range ~1.2V

- Narrow Bus Reduces Cable Size and Cost

- High Throughput: 1.785Gbps

- Up to 595Mbps per Channel

- Internal PLL with No External ponents

- patible with TIA/EIA-644 Specification

- Offered in 48-lead TSSOP Packages