56F805 Description

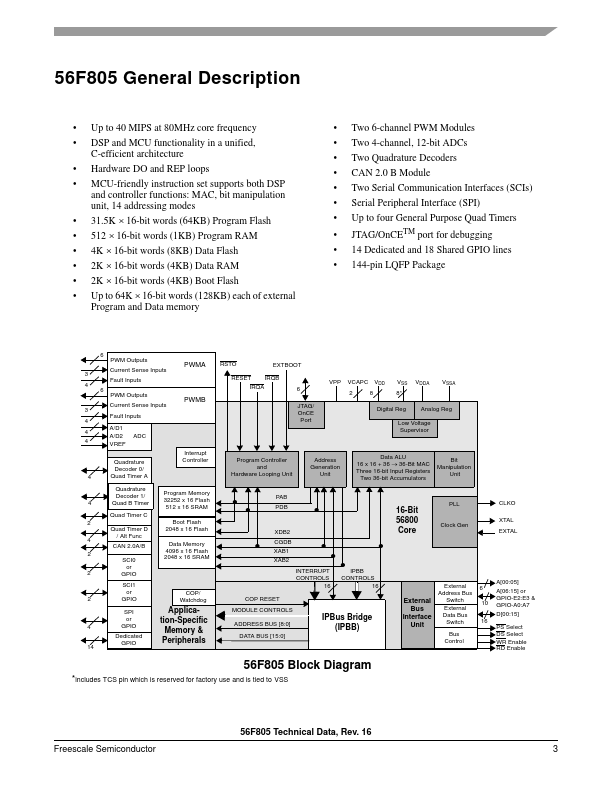

of Change Added revision history. Added this text to footnote 2 in Table 3-8: “However, the high pulse width does not have to be any particular percent of the low pulse width.” 56F805 General Description Up to 40 MIPS at 80MHz core frequency DSP and MCU functionality in a unified, C-efficient architecture Hardware DO and REP loops MCU-friendly instruction set supports both DSP and controller functions:.

56F805 Key Features

- Efficient 16-bit 56800 family processor engine with dual Harvard architecture

- As many as 40 Million Instructions Per Second (MIPS) at 80MHz core frequency

- Single-cycle 16 × 16-bit parallel Multiplier-Accumulator (MAC)

- Two 36-bit accum