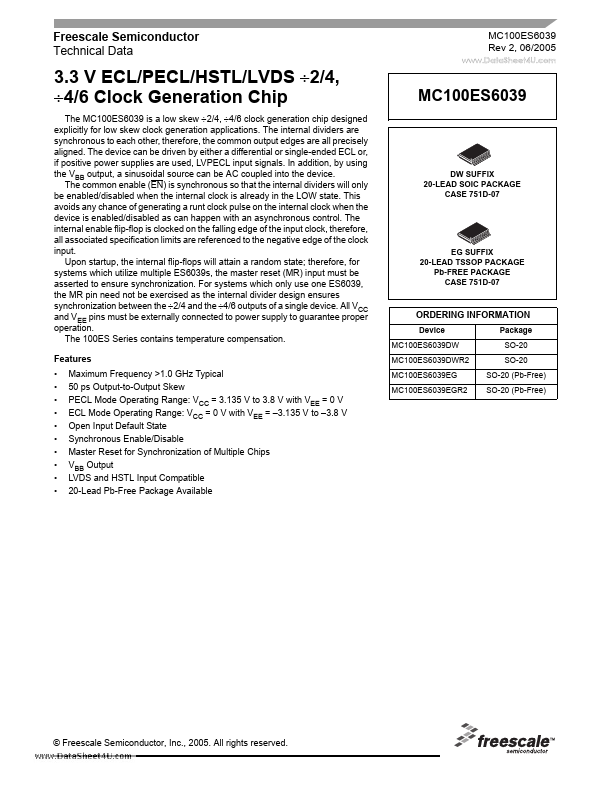

MC100ES6039

MC100ES6039 is 3.3V ECL/PECL/HSTL/LVDS Generation Chip manufactured by Freescale Semiconductor.

Freescale Semiconductor Technical Data

MC100ES6039 Rev 2, 06/2005

..

3.3 V ECL/PECL/HSTL/LVDS ÷2/4, ÷4/6 Clock Generation Chip

The MC100ES6039 is a low skew ÷2/4, ÷4/6 clock generation chip designed explicitly for low skew clock generation applications. The internal dividers are synchronous to each other, therefore, the mon output edges are all precisely aligned. The device can be driven by either a differential or single-ended ECL or, if positive power supplies are used, LVPECL input signals. In addition, by using the VBB output, a sinusoidal source can be AC coupled into the device. The mon enable (EN) is synchronous so that the internal dividers will only be...