MC100ES6221

Overview

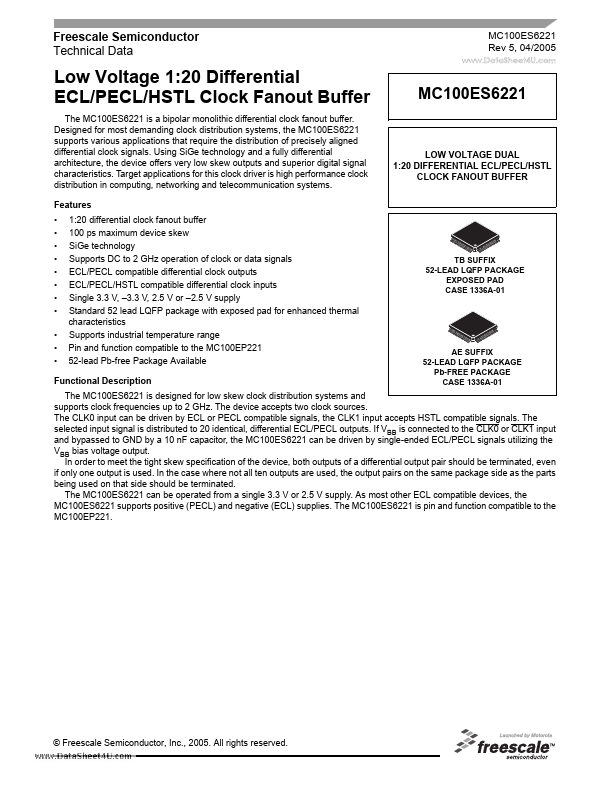

- 1:20 differential clock fanout buffer 100 ps maximum device skew SiGe technology Supports DC to 2 GHz operation of clock or data signals ECL/PECL compatible differential clock outputs ECL/PECL/HSTL compatible differential clock inputs Single 3.3 V, -3.3 V, 2.5 V or -2.5 V supply Standard 52 lead LQFP package with exposed pad for enhanced thermal characteristics Supports industrial temperature range Pin and function compatible to the MC100EP221 52-lead Pb-free Package Available