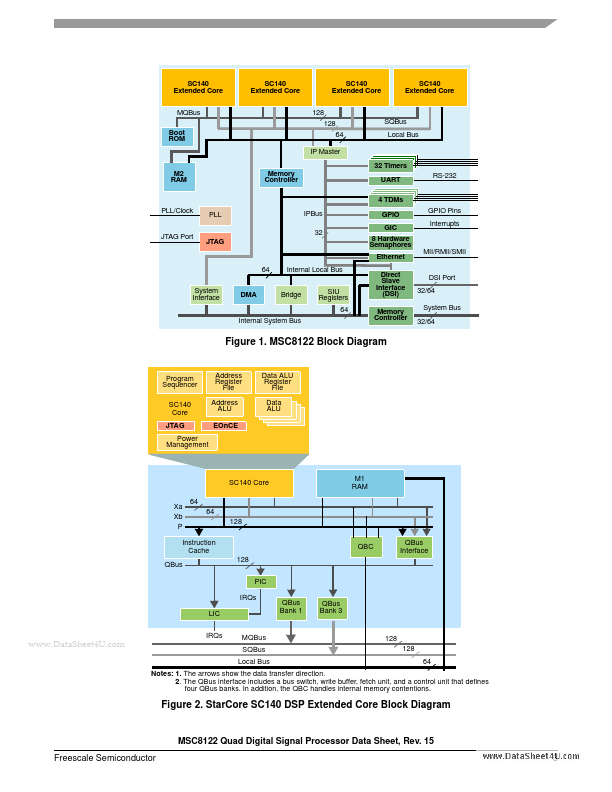

MSC8122 Description

Freescale Semiconductor Data Sheet: 475 Kbyte M2 memory for critical data and temporary data buffering. M2-accessible multi-core MQBus connecting the M2 memory with all four cores, operating at the core frequency, with data bus access of up to 128-bit reads and up to 64-bit writes, central efficient round-robin arbiter for core access to the bus, and atomic operation control of M2 memory access by the cores and the...