MSC8256 Description

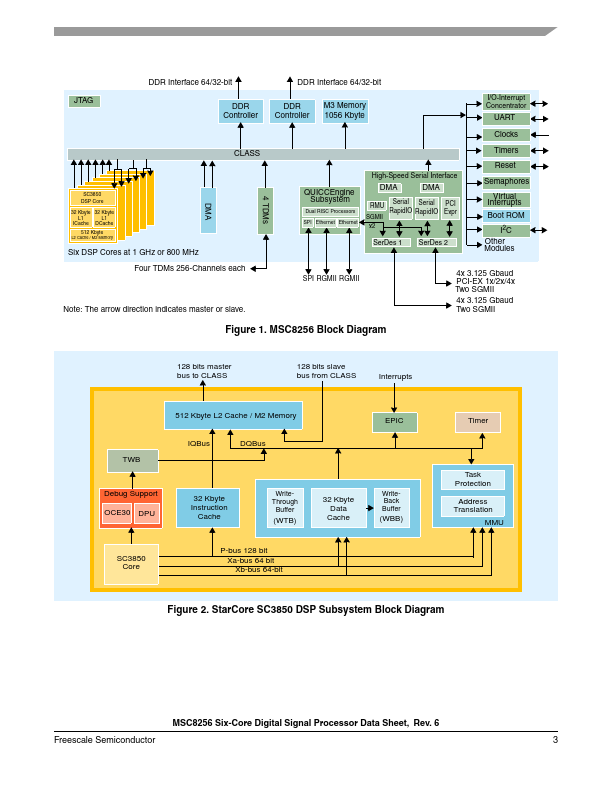

Freescale Semiconductor Data Sheet Six-Core Digital Signal Processor Document Number: Chip-level arbitration and switching system (CLASS) that provides full fabric non-blocking arbitration between the cores and other initiators and the M2 memory, shared M3 memory, DDR SRAM controllers, device configuration control and status registers, and other targets. 1056 Kbyte 128-bit wide M3 memory, 1024 Kbytes of which can be...