P3041 Description

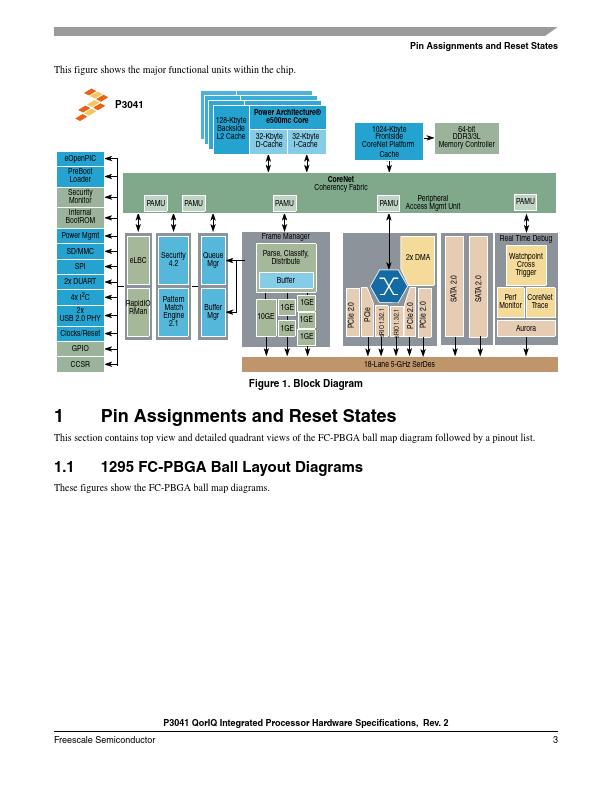

Freescale Semiconductor Data Sheet: Technical Data Document Number: 2, 02/2013 P3041 P3041 QorIQ Integrated Processor Hardware Specifications The P3041 QorIQ integrated processor utilizes four processor cores built on Power Architecture® technology.

P3041 Key Features

- Four e500mc Power Architecture cores, each with a backside 128 KB L2 cache with ECC

- Three levels of instructions: User, supervisor, and hypervisor

- Independent boot and reset

- Secure boot capability

- CoreNet fabric supporting coherent and non-coherent transactions amongst CoreNet end-points

- CoreNet platform cache with ECC

- CoreNet bridges between the CoreNet fabric the I/Os, datapath accelerators, and high and low speed peripheral interfaces

- One 10-Gigabit Ethernet (XAUI) controller

- Five 1-Gigabit Ethernet controllers

- SGMII interfaces

P3041 Applications

- Four e500mc Power Architecture cores, each with a backside 128 KB L2 cache with ECC