Datasheet Summary

..

Freescale Semiconductor Hardware Specification

MCF5271EC Rev. 1.2, 12/2004

MCF5271 Integrated Microprocessor Hardware Specification

32-bit Embedded Controller Division

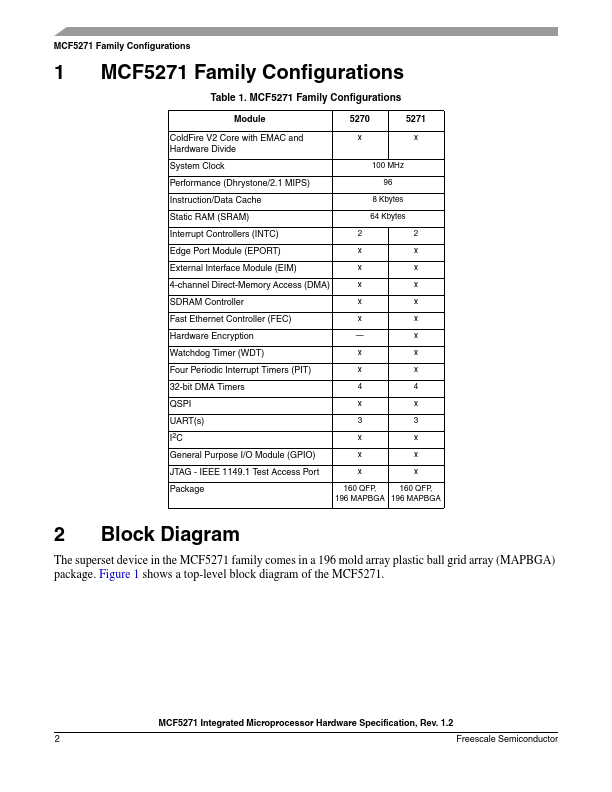

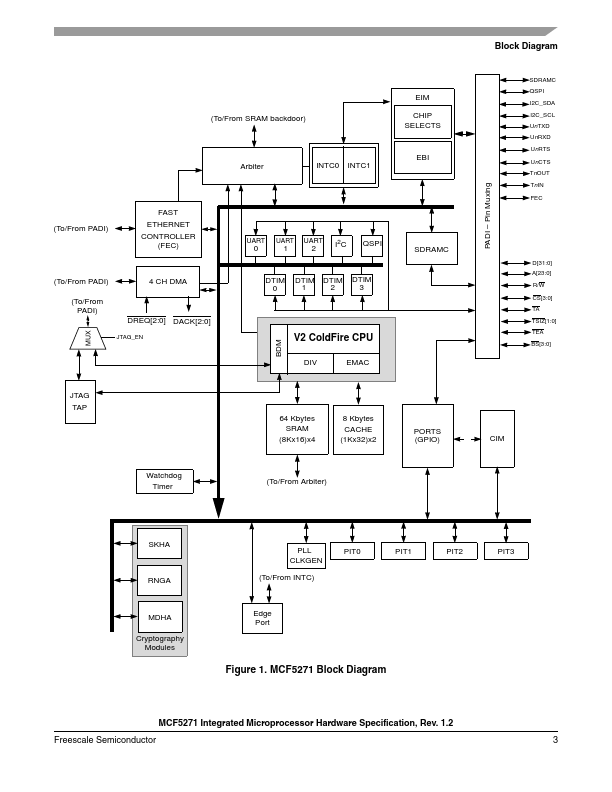

The MCF5271 family is a highly integrated implementation of the ColdFire® family of reduced instruction set puting (RISC) microprocessors. This document describes pertinent Features and functions of the MCF5271 family. The MCF5271 family includes the MCF5271 and MCF5270 microprocessors. The differences between these parts are summarized below in Table 1. This document is written from the perspective of the MCF5271 and unless otherwise noted, the information applies also to the MCF5270. The MCF5271...