Description

Type Comments SA Synchronous Address Inputs Input - R/W Synchronous Read Input High: Read Low: Write BW0-BW3 Synchronous Byte Writes Input Active Low LD Synchronous Load Pin Input Active Low K Input Clock Input Active High K Input Clock Input Active Low TMS Test Mode Select Input - TDI Test Data Input Input - TCK Test Clock Input Input - TDO Test Data Output Output - VREF HSTL Input Reference Voltage Input - ZQ Output Impedance Matching Input Input - MCL Must Connect Low -- DQ Data I/O Input/Output Three State Doff Disable DLL when low Input Active Low CQ Output Echo Clock Output - CQ Output Echo Clock Output - VDD Power Supply Supply 1.8 V Nominal VDDQ Isolated Output Buffer Supply Supply 1.8 V or 1.5 V Nominal VSS Power Supply: Ground Supply - QVLD Q Valid Output Output - ODT On-Die Termination Input Low = Low Impedance Range High/Float = High Impedance Range NC No Connect -- Notes: 1. NC = Not Connected to die or any other pin 2.

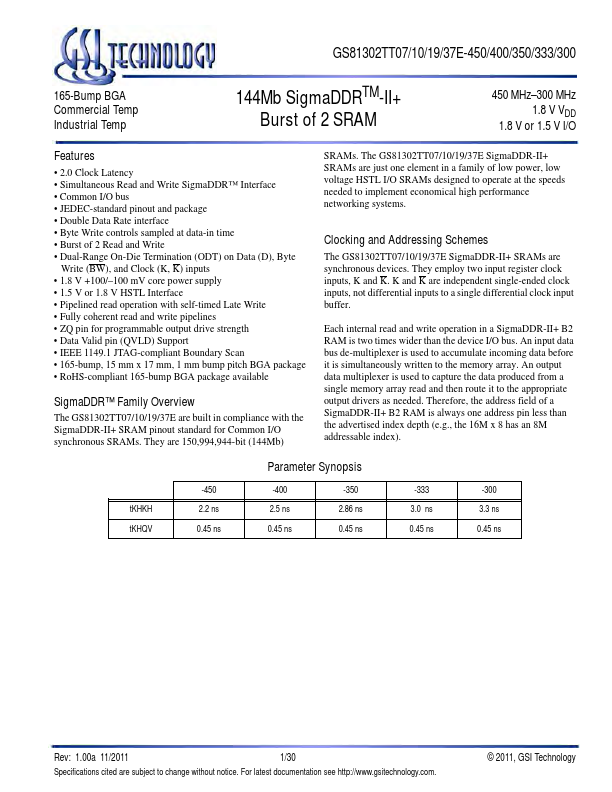

Key Features

- 2.0 Clock Latency

- Simultaneous Read and Write SigmaDDR™ Interface

- Common I/O bus

- JEDEC-standard pinout and package

- Double Data Rate interface

- Byte Write controls sampled at data-in time

- Burst of 2 Read and Write

- Dual-Range On-Die Termination (ODT) on Data (D), Byte Write (BW), and Clock (K, K) inputs

- 1.8 V +100/-100 mV core power supply

- 1.5 V or 1.8 V HSTL Interface