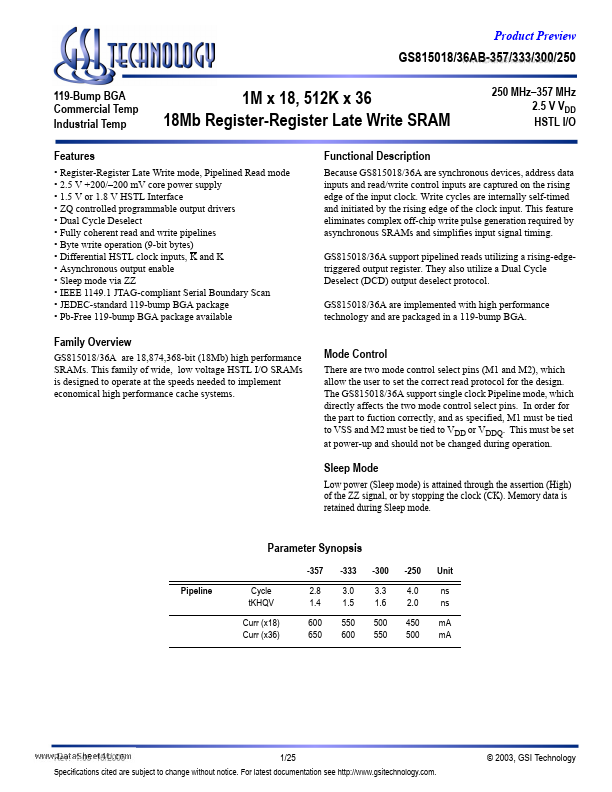

GS815018AB-250 Description

250 MHz 357 MHz 2.5 V VDD HSTL I/O Because GS815018/36A are synchronous devices, address data inputs and read/write control inputs are captured on the rising edge of the input clock. Write cycles are internally self-timed and initiated by the rising edge of the clock input.

GS815018AB-250 Key Features

- Register-Register Late Write mode, Pipelined Read mode

- 2.5 V +200/-200 mV core power supply

- 1.5 V or 1.8 V HSTL Interface

- ZQ controlled programmable output drivers

- Dual Cycle Deselect

- Fully coherent read and write pipelines

- Byte write operation (9-bit bytes)

- Differential HSTL clock inputs, K and K

- Asynchronous output enable

- Sleep mode via ZZ