GS8170DD36C-250 Overview

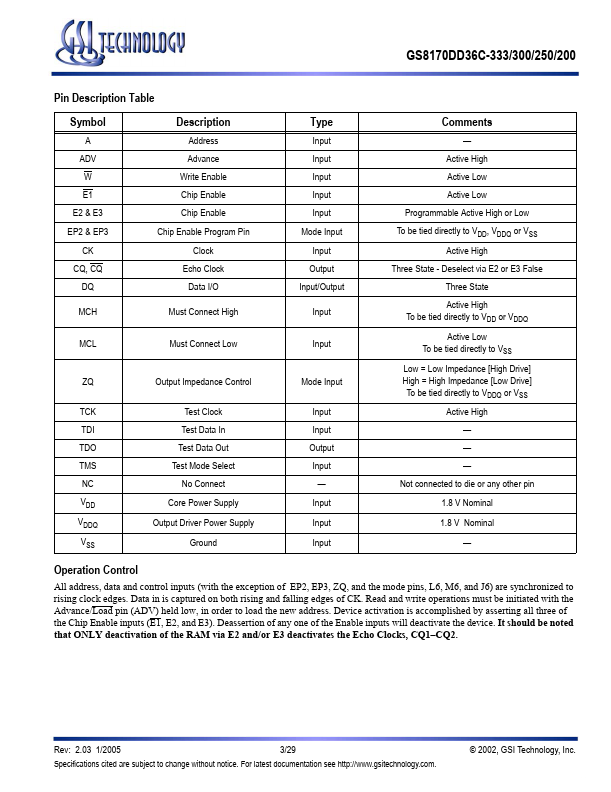

Because SigmaRAMs are synchronous devices, address data inputs and read/write control inputs are captured on the rising edge of the input clock. Write cycles are internally self-timed and initiated by the rising edge of the clock input.

GS8170DD36C-250 Key Features

- Double Data Rate Read and Write mode

- Late Write; Pipelined read operation

- JEDEC-standard SigmaRAM™ pinout and package

- 1.8 V +150/-100 mV core power supply

- 1.8 V CMOS Interface

- ZQ controlled user-selectable output drive strength

- Dual Cycle Deselect

- Burst Read and Write option

- Fully coherent read and write pipelines

- Echo Clock outputs track data output drivers