GS8321Z32GE

GS8321Z32GE is 36Mb Pipelined and Flow Through Synchronous NBT SRAM manufactured by GSI Technology.

- Part of the GS8321Z18E comparator family.

- Part of the GS8321Z18E comparator family.

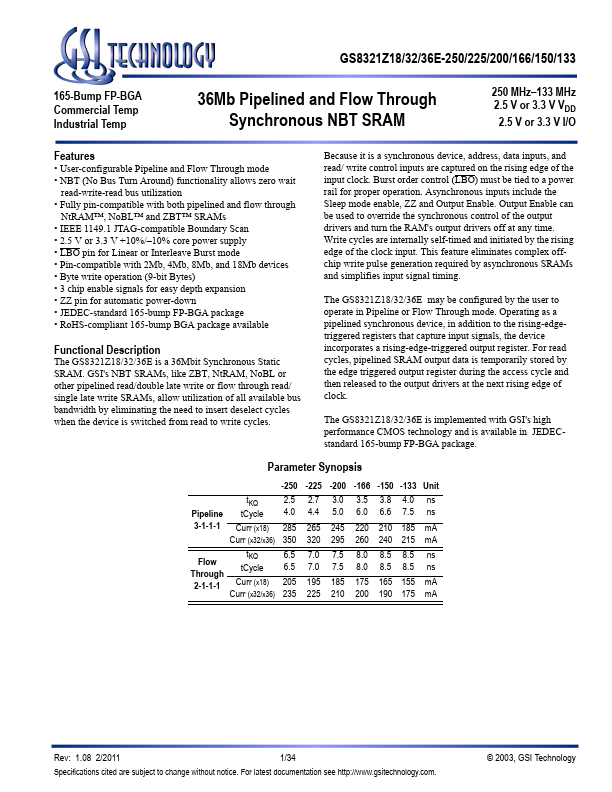

GS8321Z18/32/36E-250/225/200/166/150/133

165-Bump FP-BGA mercial Temp Industrial Temp

36Mb Pipelined and Flow Through Synchronous NBT SRAM

250 MHz- 133 MHz 2.5 V or 3.3 V VDD 2.5 V or 3.3 V I/O

Features

- User-configurable Pipeline and Flow Through mode

- NBT (No Bus Turn Around) functionality allows zero wait read-write-read bus utilization

- Fully pin-patible with both pipelined and flow through

NtRAM™, NoBL™ and ZBT™ SRAMs

- IEEE 1149.1 JTAG-patible Boundary Scan

- 2.5 V or 3.3 V +10%/- 10% core power supply

- LBO pin for Linear or Interleave Burst mode

- Pin-patible with 2Mb, 4Mb, 8Mb, and 18Mb devices

- Byte write operation (9-bit Bytes)

- 3 chip enable signals for easy...