GS864236C-xxxV

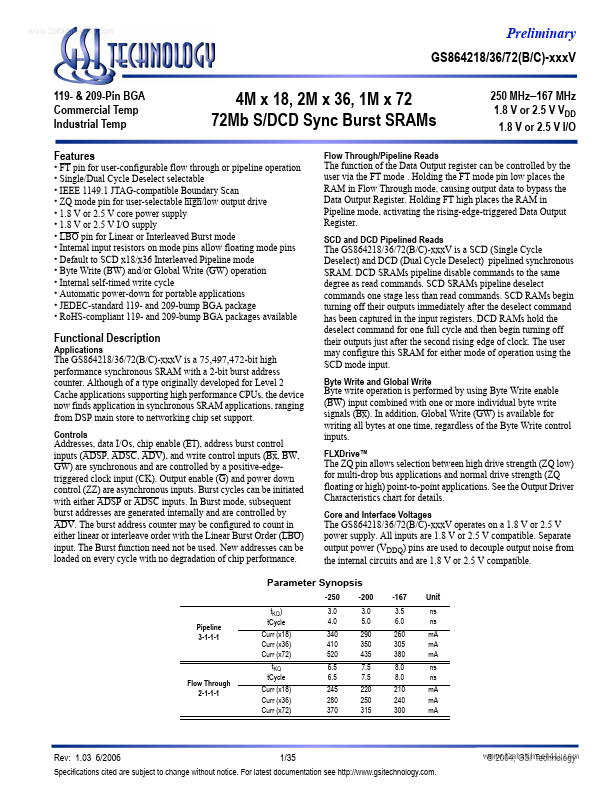

GS864236C-xxxV is 4M x 18 / 2M x 36/ 1M x 72 72Mb S/DCD Sync Burst SRAMs manufactured by GSI Technology.

- Part of the GS864218B-xxxV comparator family.

- Part of the GS864218B-xxxV comparator family.

Features

4M x 18, 2M x 36, 1M x 72 72Mb S/DCD Sync Burst SRAMs

250 MHz- 167 MHz 1.8 V or 2.5 V VDD 1.8 V or 2.5 V I/O

- FT pin for user-configurable flow through or pipeline operation

- Single/Dual Cycle Deselect selectable

- IEEE 1149.1 JTAG-patible Boundary Scan

- ZQ mode pin for user-selectable high/low output drive

- 1.8 V or 2.5 V core power supply

- 1.8 V or 2.5 V I/O supply

- LBO pin for Linear or Interleaved Burst mode

- Internal input resistors on mode pins allow floating mode pins

- Default to SCD x18/x36 Interleaved Pipeline mode

- Byte Write (BW) and/or Global Write (GW) operation

- Internal self-timed write cycle

- Automatic power-down for portable applications

- JEDEC-standard 119- and 209-bump BGA package

- Ro HS-pliant 119- and 209-bump BGA packages available

Flow Through/Pipeline Reads The function of the Data Output register can be controlled by the user via the FT mode . Holding the FT mode pin low places the RAM in Flow Through mode, causing output data to bypass the Data Output Register. Holding FT high places the RAM in Pipeline mode, activating the rising-edge-triggered Data Output Register. SCD and DCD Pipelined Reads The GS864218/36/72(B/C)-xxx V is a SCD (Single Cycle Deselect) and DCD (Dual Cycle Deselect) pipelined synchronous SRAM. DCD SRAMs pipeline disable mands to the same degree as read mands. SCD SRAMs pipeline deselect mands one stage less than read mands. SCD RAMs begin turning off their outputs immediately after the deselect mand has been captured in the input registers. DCD RAMs hold the deselect mand for one full cycle and then begin turning off their outputs just after the second rising edge of clock. The user may configure this SRAM for either mode of operation using the SCD mode input. Byte Write and Global Write Byte write operation is performed by using Byte Write enable (BW) input bined with one or more individual byte write signals (Bx). In addition, Global Write (GW) is available for writing all bytes at one time,...