GS880F18T-14 Description

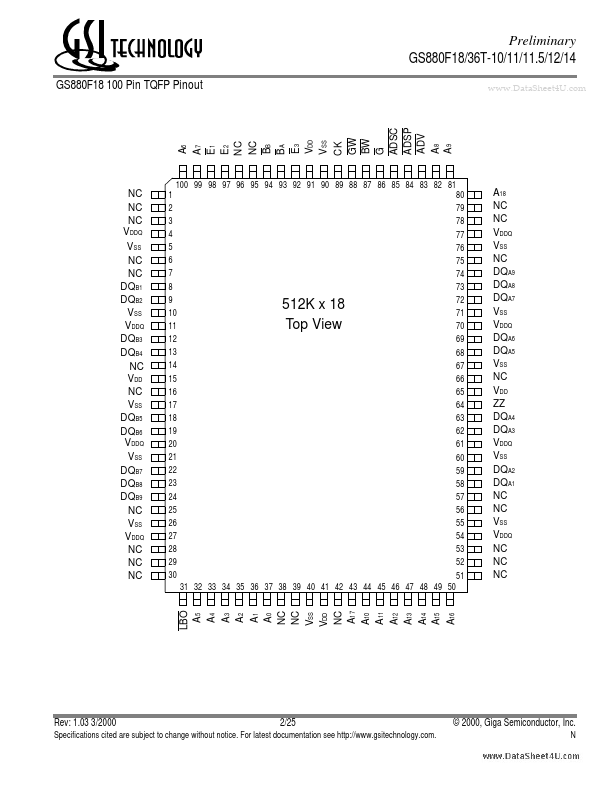

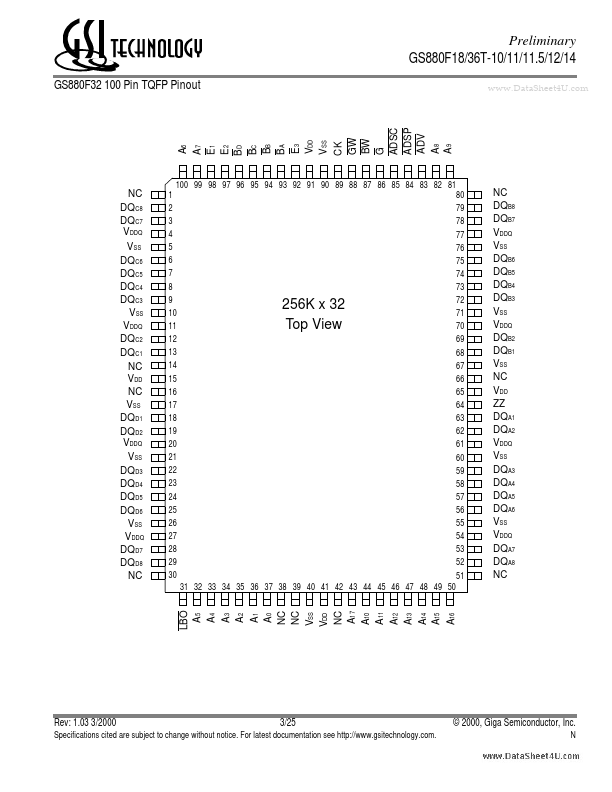

Although of a type originally developed for Level 2 Cache applications supporting high performance CPU’s, the device now finds application in synchronous SRAM applications ranging from DSP main store to networking chip set support. Controls Addresses, data I/O’s, chip enables (E1, E2, E3), address burst control inputs (ADSP, ADSC, ADV) and write control inputs (Bx, BW, GW) are synchronous and are controlled by a...

GS880F18T-14 Key Features

- Flow through mode operation

- 3.3V +10%/-5% Core power supply

- 2.5V or 3.3V I/O supply

- LBO pin for linear or interleaved burst mode

- Internal input resistors on mode pins allow floating mode pins. Default to Interleaved Pipelined Mode

- Byte write (BW) and/or global write (GW) operation

- mon data inputs and data outputs

- Clock Control, registered, address, data, and control

- Internal Self-Timed Write cycle

- Automatic power-down for portable