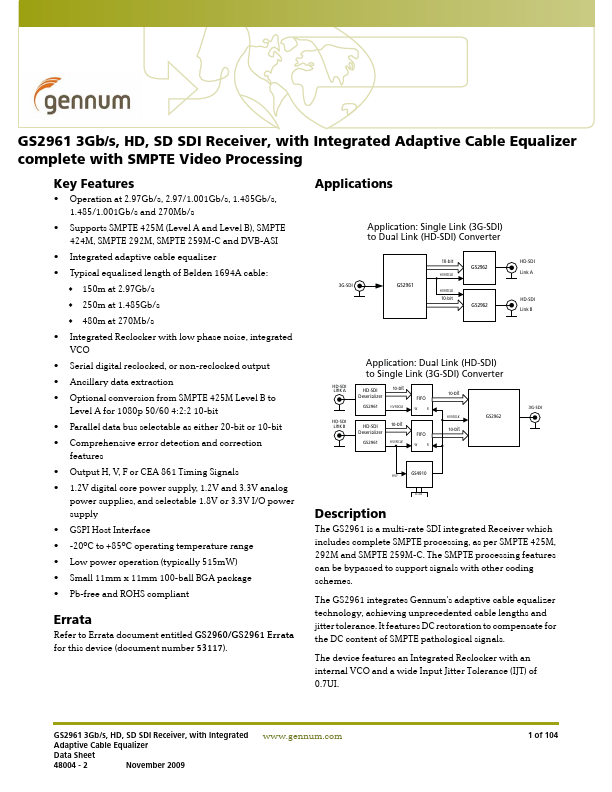

GS2961 Description

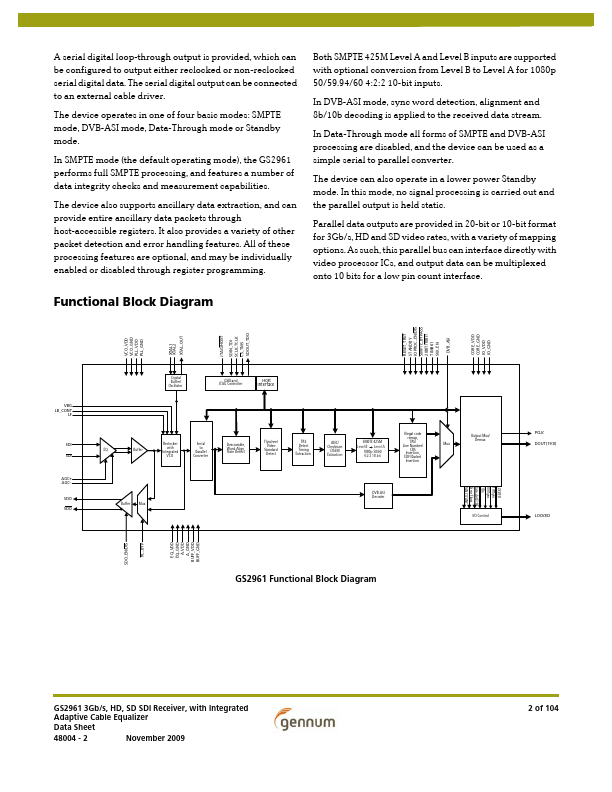

The GS2961 is a multi-rate SDI integrated Receiver which includes plete SMPTE processing, as per SMPTE 425M, 292M and SMPTE 259M-C.

GS2961 Key Features

- Operation at 2.97Gb/s, 2.97/1.001Gb/s, 1.485Gb/s, 1.485/1.001Gb/s and 270Mb/s

- Supports SMPTE 425M (Level A and Level B), SMPTE 424M, SMPTE 292M, SMPTE 259M-C and DVB-ASI

- Integrated adaptive cable equalizer

- Typical equalized length of Belden 1694A cable

- 150m at 2.97Gb/s

- 250m at 1.485Gb/s

- 480m at 270Mb/s

- Integrated Reclocker with low phase noise, integrated VCO

- Serial digital reclocked, or non-reclocked output

- Ancillary data extraction