HI-6130 Overview

Key Specifications

Operating Voltage: 3.3 V

Max Voltage (typical range): 3.45 V

Min Voltage (typical range): 3.15 V

Max Frequency: 50.005 MHz

Description

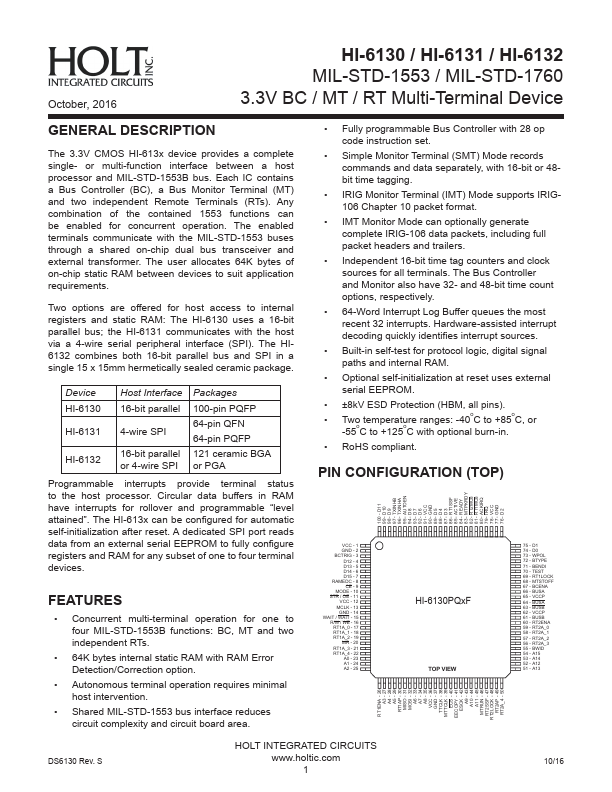

The 3.3V CMOS HI-613x device provides a complete single- or multi-function interface between a host processor and MIL-STD-1553B bus. Each IC contains a Bus Controller (BC), a Bus Monitor Terminal (MT) and two independent Remote Terminals (RTs).

Key Features

- Concurrent multi-terminal operation for one to four MIL-STD-1553B functions: BC, MT and two independent RTs

- 64K bytes internal static RAM with RAM Error Detection/Correction option

- Autonomous terminal operation requires minimal host intervention

- Shared MIL-STD-1553 bus interface reduces circuit complexity and circuit board area. RT1ENA