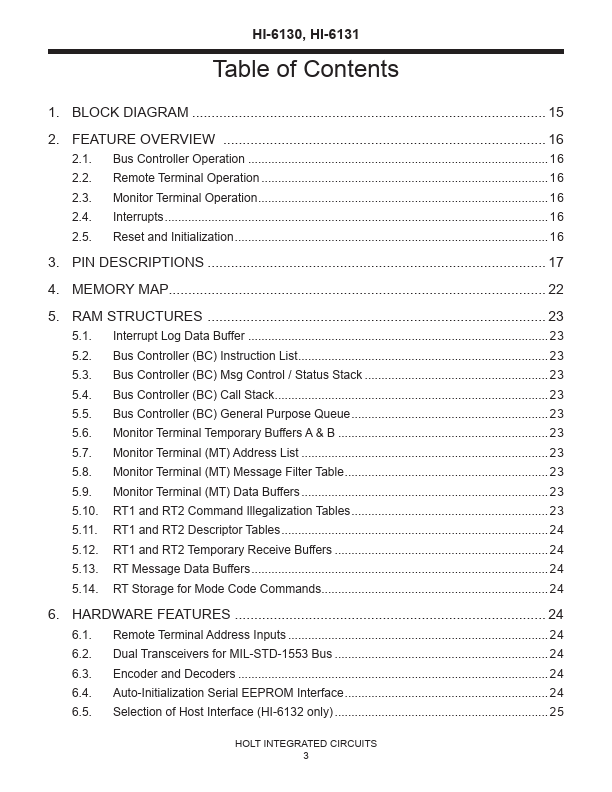

Datasheet Summary

October, 2016

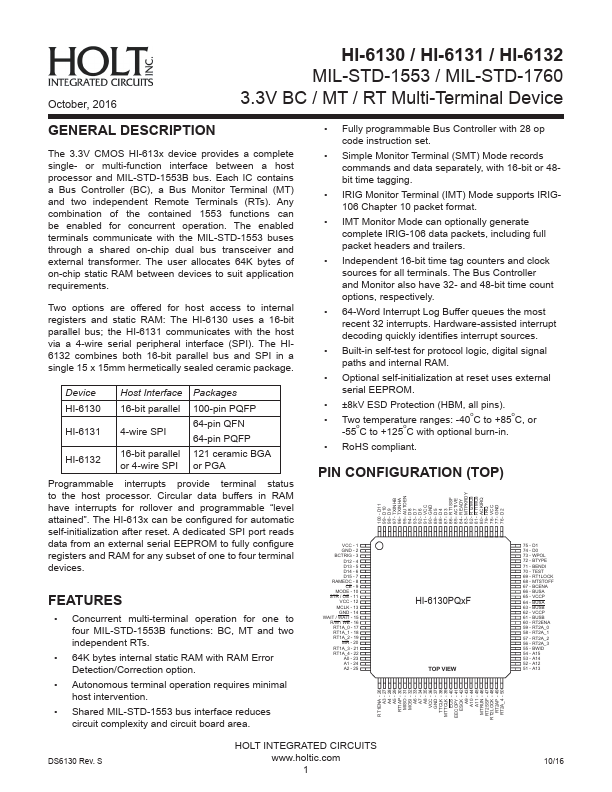

HI-6130 / HI-6131 / HI-6132 MIL-STD-1553 / MIL-STD-1760 3.3V BC / MT / RT Multi-Terminal Device

GENERAL DESCRIPTION

The 3.3V CMOS HI-613x device provides a plete single- or multi-function interface between a host processor and MIL-STD-1553B bus. Each IC contains a Bus Controller (BC), a Bus Monitor Terminal (MT) and two independent Remote Terminals (RTs). Any bination of the contained 1553 functions can be enabled for concurrent operation. The enabled terminals municate with the MIL-STD-1553 buses through a shared on-chip dual bus transceiver and external transformer. The user allocates 64K bytes of on-chip static RAM between devices to suit application...