82C37A Overview

Description

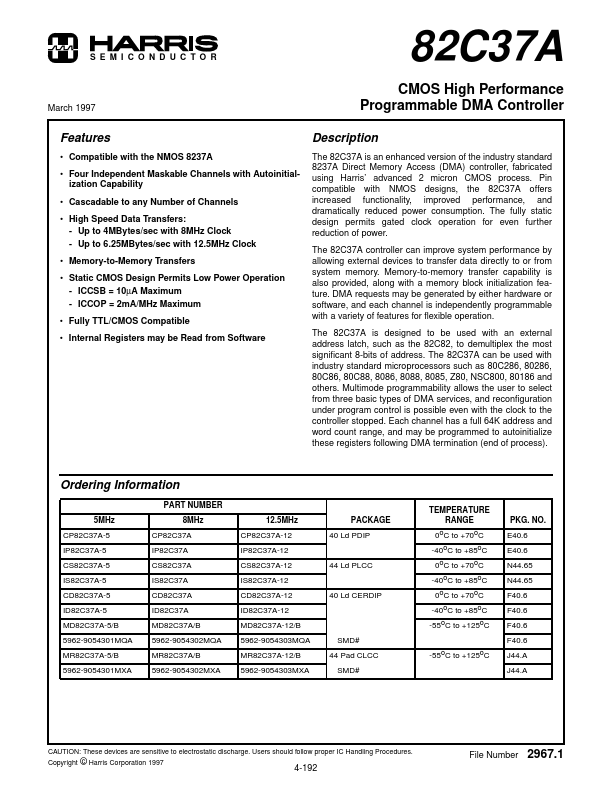

Compatible with the NMOS 8237A - Four Independent Maskable Channels with Autoinitialization Capability - Cascadable to any Number of Channels - High Speed Data Transfers: - Up to 4MBytes/sec with 8MHz Clock - Up to 6.25MBytes/sec with 12.5MHz Clock - Memory-to-Memory Transfers - Static CMOS Design Permits Low Power Operation - ICCSB = 10µA Maximum - ICCOP = 2mA/MHz Maximum - Fully TTL/CMOS Compatible - Internal Registers may be Read from Software The 82C37A is an enhanced version of the industry standard 8237A Direct Memory Access (DMA) controller, fabricated using Harris’ advanced 2 micron CMOS process. Pin compatible with NMOS designs, the 82C37A offers increased functionality, improved performance, and dramatically reduced power consumption.