HD74HC294 Overview

Key Specifications

Package: SOP

Operating Voltage: 4.5 V

Max Voltage (typical range): 6 V

Min Voltage (typical range): 2 V

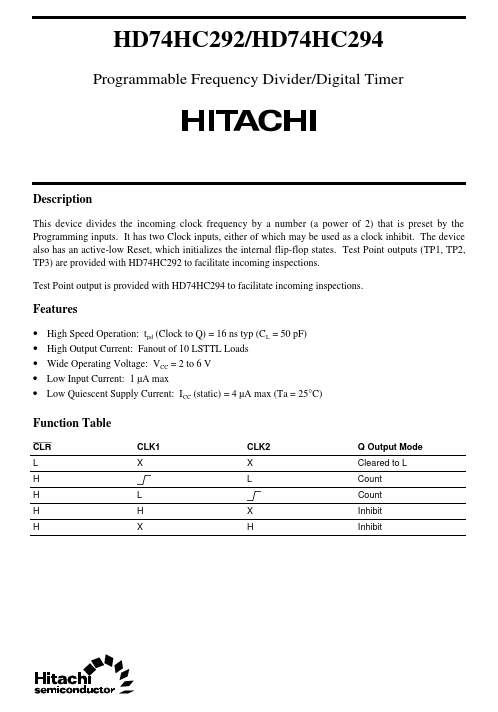

Description

This device divides the incoming clock frequency by a number (a power of 2) that is preset by the Programming inputs. It has two Clock inputs, either of which may be used as a clock inhibit.