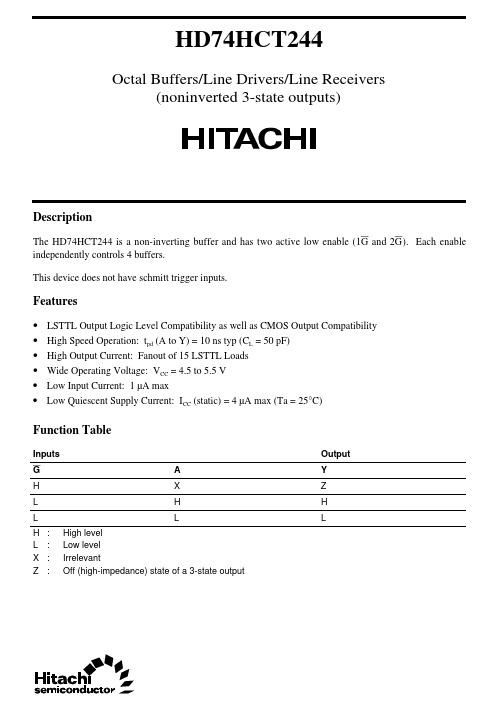

| Part | HD74HCT244 |

|---|---|

| Description | Octal Buffers/Line Drivers/Line Receivers(noninverted 3-state outputs) |

| Manufacturer | Hitachi Semiconductor |

| Size | 58.39 KB |

Related Datasheets

| Part Number | Manufacturer | Description |

|---|---|---|

| CBT16211 | NXP Semiconductors | OCTAL TRANSPARENT D-TYPE LATCHES WITH 3-STATE OUTPUTS |

| CD43-4R7 | Linear Technology | Dual Micropower DC/DC Converter with Positive and Negative Outputs |

| NJU3427 | New Japan Radio | 36 Outputs VFD Controller/Driver |