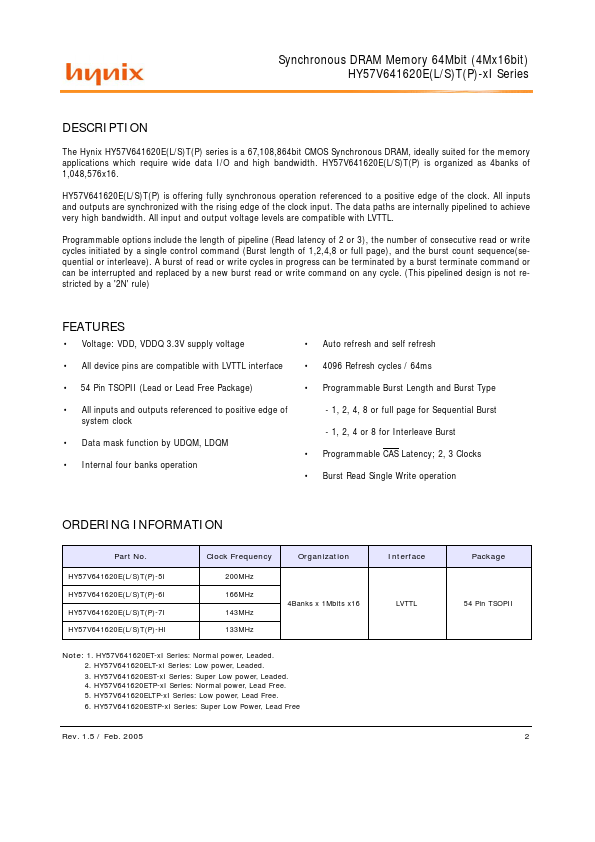

HY57V641620ET Description

and is subject to change without notice. Hynix does not assume any responsibility for use of circuits described. No patent licenses are implied.

HY57V641620ET Key Features

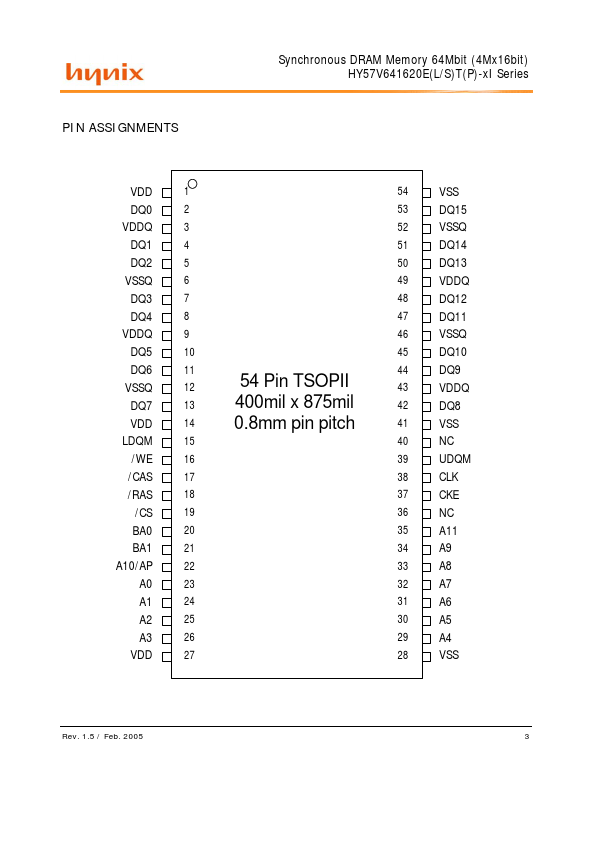

- Voltage: VDD, VDDQ 3.3V supply voltage All device pins are patible with LVTTL interface 54 Pin TSOPII (Lead or Lead Free

- Internal four banks operation

- Burst Read Single Write operation Programmable CAS Latency; 2, 3 Clocks

- Auto refresh and self refresh 4096 Refresh cycles / 64ms Programmable Burst Length and Burst Type

- 1, 2, 4, 8 or full page for Sequential Burst