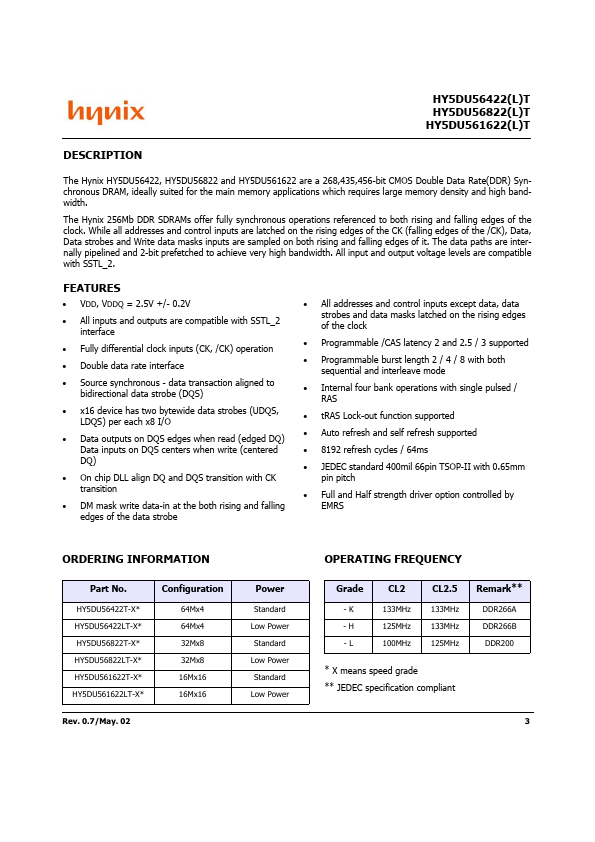

HY5DU56822T Description

and is subject to change without notice. does not assume any responsibility for use of circuits described. No patent licenses are implied.

HY5DU56822T Key Features

- VDD, VDDQ = 2.5V +/- 0.2V All inputs and outputs are patible with SSTL_2 interface Fully differential clock inputs (CK,

- data transaction aligned to bidirectional data strobe (DQS) x16 device has two bytewide data strobes (UDQS, LDQS) per ea