HYMD132645BL8-L Key Features

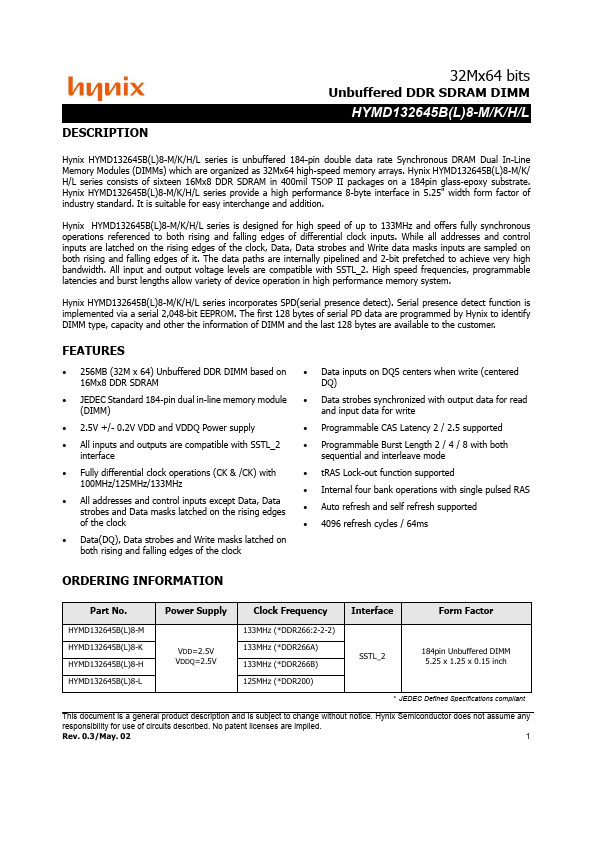

- 256MB (32M x 64) Unbuffered DDR DIMM based on 16Mx8 DDR SDRAM

- JEDEC Standard 184-pin dual in-line memory module (DIMM)

- 2.5V +/- 0.2V VDD and VDDQ Power supply

- All inputs and outputs are patible with SSTL_2 interface

- Fully differential clock operations (CK & /CK) with 100MHz/125MHz/133MHz

- All addresses and control inputs except Data, Data strobes and Data masks latched on the rising edges of the clock

- Data(DQ), Data strobes and Write masks latched on both rising and falling edges of the clock

- Data inputs on DQS centers when write (centered DQ)

- Data strobes synchronized with output data for read and input data for write

- Programmable CAS Latency 2 / 2.5 supported