X25170 Overview

Description

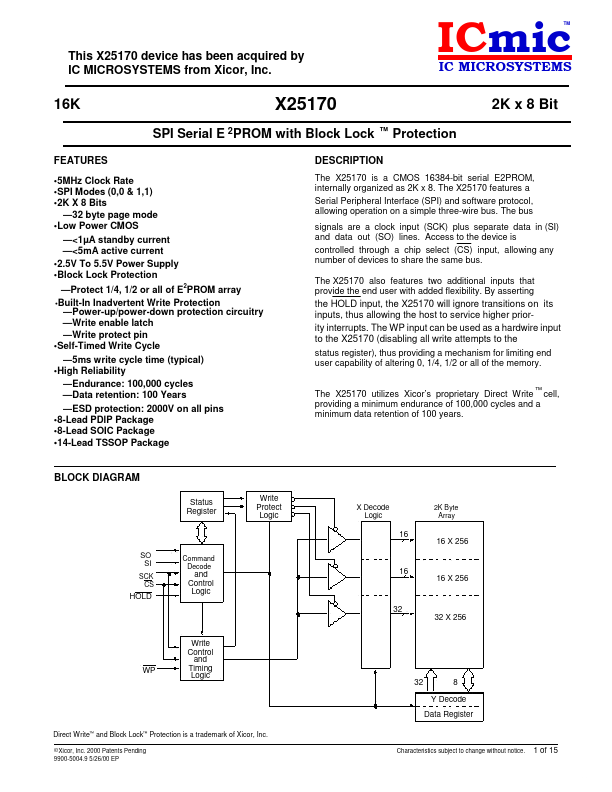

The X25170 is a CMOS 16384-bit serial E2PROM, internally organized as 2K x 8. The X25170 features a Serial Peripheral Interface (SPI) and software protocol, allowing operation on a simple three-wire bus.

Key Features

- 5MHz Clock Rate

- SPI Modes (0,0 & 1,1)

- 2K X 8 Bits -32 byte page mode

- Low Power CMOS -<1µA standby current -<5mA active current

- 2.5V To 5.5V Power Supply

- Block Lock Protection -Protect 1/4, 1/2 or all of E2PROM array

- Built-In Inadvertent Write Protection -Power-up/power-down protection circuitry -Write enable latch -Write protect pin

- Self-Timed Write Cycle -5ms write cycle time (typical)

- High Reliability -Endurance: 100,000 cycles -Data retention: 100 Years -ESD protection: 2000V on all pins

- 8-Lead PDlP Package