ICS844001-21

ICS844001-21 is CRYSTAL-TO-LVDS FREQUENCY SYNTHESIZER manufactured by ICS.

DESCRIPTION

The ICS844001-21 is a a highly versatile, low IC S phase noise LVDS Synthesizer which can generate Hi Per Clock S™ low jitter reference clocks for a var iety of munications applications and is a member of the Hi Per Clocks TM family of high performance clock solutions from IDT. The dual crystal interface allows the synthesizer to support up to two munications standards in a given application (i.e. 1GB Ethernet with a 25MHz crystal and 1Gb Fibre Channel using a 25.5625MHz crystal). The rms phase jitter performance is typically less than 1ps, thus making the device acceptable for use in demanding applications such as OC48 SONET and 10Gb Ethernet. The ICS844001-21 is packaged in a small 24-pin TSSOP package.

FEATURES

- One differential LVDS output pair and one LVCMOS reference output

- Selectable crystal oscillator interface or LVCMOS/LVTTL single-ended input

- VCO range: 560MHz

- 700MHz

- Supports the following applications: SONET, Ethernet, Fibre Channel, Serial ATA, and HDTV

- RMS phase jitter @ 622.08MHz (12k Hz

- 20MHz): 0.92ps (typical)

- Full 3.3V supply mode

- 0°C to 70°C ambient operating temperature

- Available in both standard (Ro HS 5) and lead-free (Ro HS 6) packages

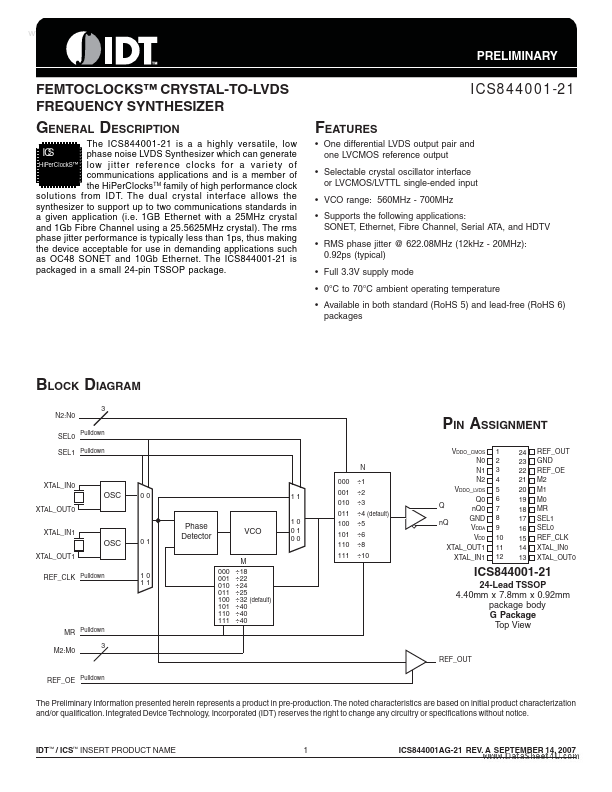

BLOCK DIAGRAM

3 N2:N0 SEL0 Pulldown SEL1 Pulldown N XTAL_IN0 000 001 010 011 100 101 110 111 ÷1 ÷2 ÷3 ÷4 (default) ÷5 ÷6 ÷8 ÷10

PIN ASSIGNMENT

VDDO_CMOS N0 N1 N2 VDDO_LVDS Q0 Q n Q0 GND n Q VDDA VDD XTAL_OUT1 XTAL_IN1 1 2 3 4 5 6 7 8 9 10 11 12 24 23 22 21 20 19 18 17 16 15 14 13 REF_OUT GND REF_OE M2 M1 M0 MR SEL1 SEL0 REF_CLK XTAL_IN0 XTAL_OUT0

XTAL_OUT0 XTAL_IN1

XTAL_OUT1 REF_CLK Pulldown

Phase Detector

10 01 00

10 11

000 001 010 011 100 101 110 111

M ÷18 ÷22 ÷24 ÷25 ÷32 (default) ÷40 ÷40 ÷40

24-Lead TSSOP 4.40mm x 7.8mm x 0.92mm package body G Package Top View

MR Pulldown M2:M0 3

REF_OUT REF_OE Pulldown

The Preliminary Information presented herein represents a product in pre-production. The noted characteristics are based on initial...