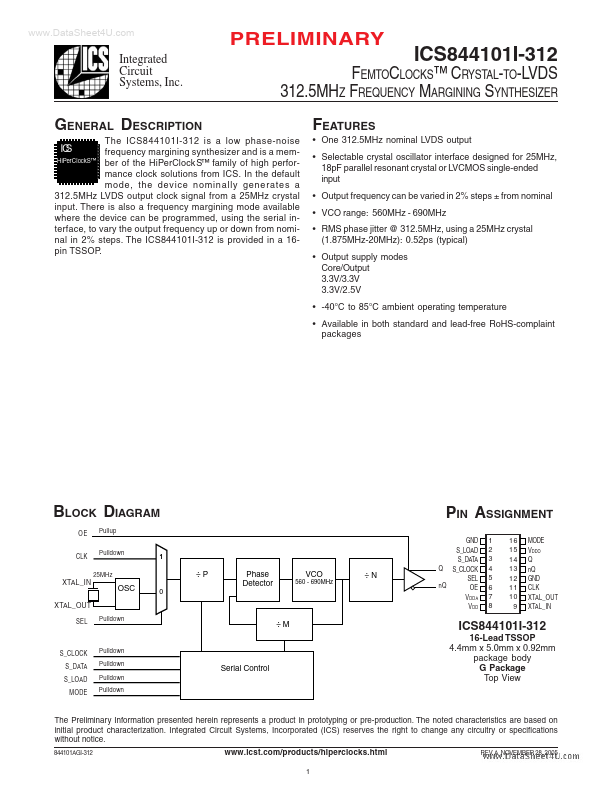

ICS844101I-312

FEATURES

- One 312.5MHz nominal LVDS output

- Selectable crystal oscillator interface designed for 25MHz, 18p F parallel resonant crystal or LVCMOS single-ended input

- Output frequency can be varied in 2% steps ± from nominal

- VCO range: 560MHz

- 690MHz

- RMS phase jitter @ 312.5MHz, using a 25MHz crystal (1.875MHz-20MHz): 0.52ps (typical)

- Output supply modes Core/Output 3.3V/3.3V 3.3V/2.5V

- -40°C to 85°C ambient operating temperature

- Available in both standard and lead-free Ro HS-plaint packages

GENERAL DESCRIPTION

The ICS844101I-312 is a low phase-noise frequency margining synthesizer and is a mem Hi Per Clock S™ ber of the Hi Per Clock S™ family of high performance clock solutions from ICS. In the default mode, the device nominally generates a 312.5MHz LVDS output clock signal from a 25MHz crystal input. There is also a frequency margining mode available where the device can be programmed, using the serial interface, to vary the output frequency up or down from nominal in 2% steps....