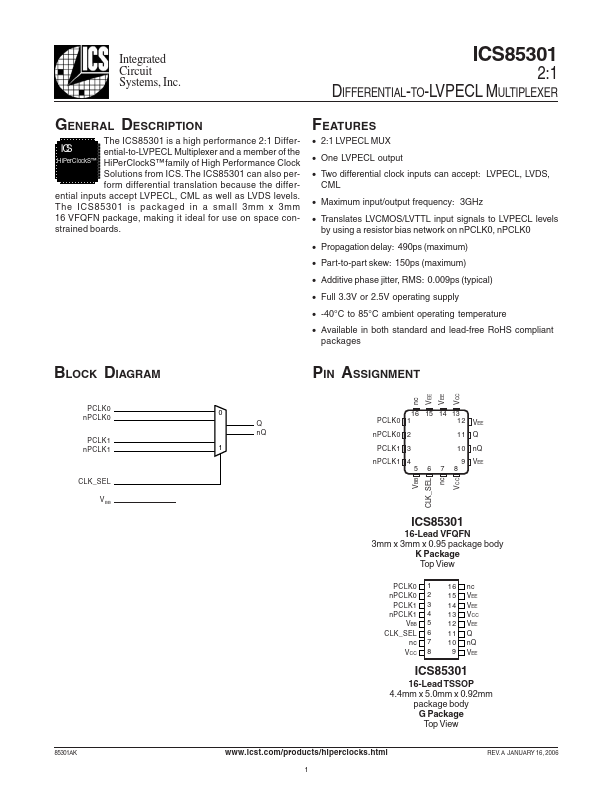

ICS85301 Key Features

- 2:1 LVPECL MUX

- One LVPECL output

- Two differential clock inputs can accept: LVPECL, LVDS, CML

- Maximum input/output frequency: 3GHz

- Translates LVCMOS/LVTTL input signals to LVPECL levels by using a resistor bias network on nPCLK0, nPCLK0

- Propagation delay: 490ps (maximum)

- Part-to-part skew: 150ps (maximum)

- Additive phase jitter, RMS: 0.009ps (typical)

- Full 3.3V or 2.5V operating supply

- 40°C to 85°C ambient operating temperature