PEEL22CV10AZ-25

PEEL22CV10AZ-25 is CMOS Programmable Electrically Erasable Logic Device manufactured by ICT.

- Part of the PEEL22CV10AZ comparator family.

- Part of the PEEL22CV10AZ comparator family.

PEEL™ 22CV10AZ-25 CMOS Programmable Electrically Erasable Logic Device

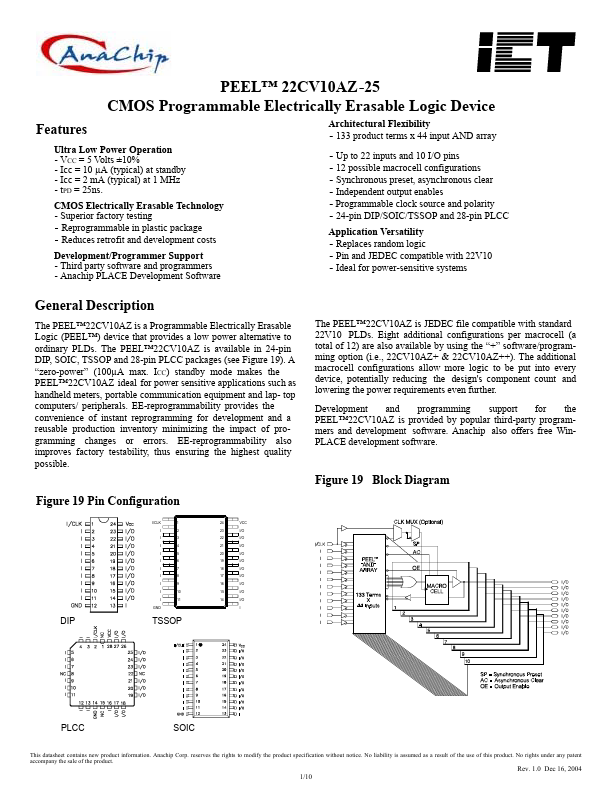

Features

Ultra Low Power Operation

- VCC = 5 Volts ±10%

- Icc = 10 µA (typical) at standby

- Icc = 2 mA (typical) at 1 MHz

- tPD = 25ns. CMOS Electrically Erasable Technology

- Superior factory testing

- Reprogrammable in plastic package

- Reduces retrofit and development costs

Development/Programmer Support

- Third party software and programmers

- Anachip PLACE Development Software

Architectural Flexibility

- 133 product terms x 44 input AND array

- Up to 22 inputs and 10 I/O pins

- 12 possible macrocell configurations

- Synchronous preset, asynchronous clear

- Independent output enables

- Programmable clock source...