9DBV0241

9DBV0241 is 2-Output 1.8V PCIe Gen1-2-3 Zero Delay / Fanout Buffer manufactured by IDT.

2-Output 1.8V PCIe Gen1-2-3 Zero Delay / Fanout Buffer with Zo=100ohms

Description

The 9DBV0241 is a member of IDT's 1.8V Very-Low-Power (VLP) PCIe family. The device has 2 output enables for clock management.

Remended Application

1.8V PCIe Gen1/2/3 Zero-Delay/Fan-out Buffer (ZDB/FOB)

Output Features

- 2

- 0.7V low-power HCSL-patible (LP-HCSL) DIF pairs w/ZO=100

Key Specifications

- DIF cycle-to-cycle jitter <50ps

- DIF output-to-output skew <50ps

- DIF additive phase jitter is <100fs rms for PCIe Gen3

- DIF additive phase jitter <300fs rms (12k-20MHz)

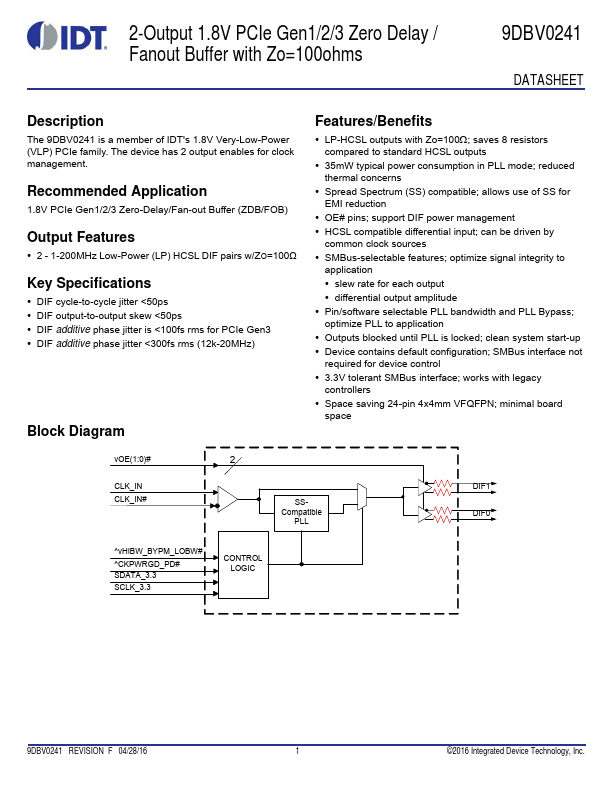

Block Diagram

Features

/Benefits

- LP-HCSL outputs with Zo=100; saves 8 resistors pared to standard HCSL...