9ZXL1930D Overview

Key Specifications

Mount Type: Surface Mount

Pins: 72

Operating Voltage: 3.3 V

Max Voltage (typical range): 3.465 V

Description

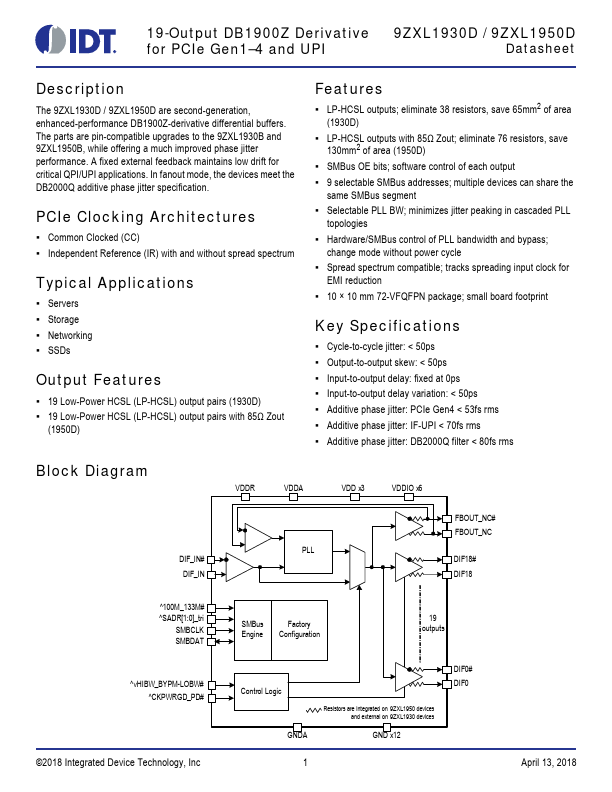

The 9ZXL1930D / 9ZXL1950D are second-generation, enhanced-performance DB1900Z-derivative differential buffers. The parts are pin-compatible upgrades to the 9ZXL1930B and 9ZXL1950B, while offering a much improved phase jitter performance.